By Luis Tellez and Stephen M. Nolan, Vidatronic, Inc.

Abstract

The design of modern Application Specific Integrated Circuits (ASICs) and Systems on a Chip (SoCs) in advanced process nodes can be differentiated by the on-die integration of analog functions, such as power management. Vidatronic offers this white paper to give some historical background on this trend and delve specifically into the integration of power management. Vidatronic IP solutions and the benefits they bring to ASIC and SoC designers are discussed.

Learn more at vidatronic.com.

Introduction & Background

Application-Specific Integrated Circuits (ASICs) are systems that are designed for specific applications and can be fully customized and optimized for specific tasks. Contrary to general-purpose integrated circuits such as microprocessors or random-access memories (RAM) in a computer, an ASIC is implemented for a particular application such as automotive, mobile, medical, home automation, industrial, IoT and others. Complex versions of an ASIC that include multiple functions, such as microprocessors, peripheral functions, and interfaces, result in a System on a Chip (SoC).

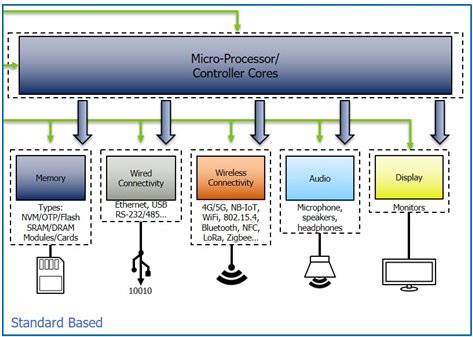

One of the most important aspects of developing a custom ASIC system is differentiating your product from other competitors in the market. Figure 1 is a block diagram showing many of the typical functions that can be included in an ASIC as an SoC design. You can see in the diagram that many of the functional blocks that are used in a typical ASIC/SoC are either standardized or highly commoditized. Utilizing commercially available IP blocks for these functions brings several benefits but no differentiation from competitor offerings. In fact, for blocks that are completely standards-driven (for example the USB interface), it is nearly impossible for there to be any differentiation.

While many blocks in an ASIC or SoC are primarily digital in nature, one way to provide market differentiation is to integrate various analog blocks. This has been a trend for over 20 years.

Figure 1: Example SoC Block Diagram

History of Analog Integration

The wafer-fab processes and CAD tools used to design and develop ASICs and SoCs tend to be optimized for logic since most of the functions on a typical system are logic. Most systems, however, require several supporting analog functions. Historically, most of those analog functions were supplied by separate, discrete catalog ICs. The drawbacks of this approach include:

- Larger packages and pin counts

- Additional printed circuit board (PCB) area

- Higher total system cost

- Lack of optimization or differentiation of the catalog analog functions

- Additional implementation complexity

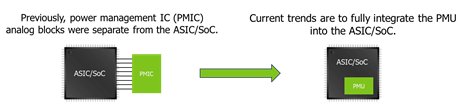

Most ASIC/SoC designs are implemented in small-geometry processes (40 nm and smaller) to take advantage of both power and die area savings. However, there are significant challenges of analog circuit design in small process linewidths due to transistor mismatch and leakage. Despite the challenges, some companies design analog functions in the small logic fabrication processes and offer them as Intellectual Property (IP) licenses for integration on-die into larger systems. As shown in Figure 2, this trend began with Serializer/De-serializer (SERDES) circuits. In the 1990s, most SoCs had wide parallel busses for external I/O that interfaced with external SERDES chips to provide the high-speed serial interfaces. Some companies worked to overcome the challenges of analog circuit design in non-optimal processes. Today, anytime a high-speed serial interface is required, the IP is available from multiple vendors for nearly every fab and process node. It is now the norm to simply license a SERDES IP and integrate it on die.

Figure 3 shows how this trend continues with other analog functions, the latest being on-die power management. Vidatronic has significant experience in overcoming the difficulties of designs in advanced-processes (down to 5 nm) and using our IP can help you get to market faster with lower risk and less cost than trying to design these circuits in house.

Figure 2: SERDES Integration Trend

Figure 3: Power Management Integration Trend

On-Die Power Management

Due to their complex design, SoCs require multiple different power supply rails providing different voltages and currents that can be powered up and down separately under careful control.

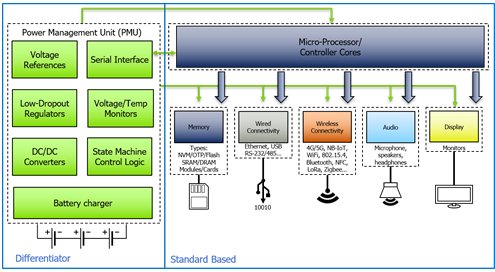

Typical functions used in power management include low dropout (LDO) linear voltage regulators, DC-DC converters, voltage references, and security functions. These functions are commonly combined into a dedicated power management unit (PMU) that supplies all of the sub-blocks. The power management blocks, in the left portion of Figure 4 below, are analog and mixed-signal circuits specialized for the application. Each of these blocks can be optimized for a given application resulting in a remarkable improvement in power and price. Descriptions are provided for the various blocks represented in the power management section of the block diagram that show how you can choose IP technology from Vidatronic that will bring substantial differentiation and value to your ASIC/SoC.

Figure 4: Example SoC Block Diagram with Integrated Power Management

Low Dropout (LDO) Regulators

LDOs are widely used to provide a regulated voltage level from a battery or other power source at the expense of a minimum voltage drop or dropout voltage (~200 mV). This small difference between the LDO input (power supply) and its regulated output voltage allows the LDO to work with very low input power supplies which has become one of the main challenges for small processes. For example, if a 1V output regulated voltage is required, the LDO can operate with an input power supply as low as 1.2V. LDO regulators also provide a very low noise and extremely stable output voltage against power supply and load variations.

Due to its closed loop architecture, many LDO circuits require a compensation scheme. Most of the LDO circuits implement a large external capacitor on their output, providing a dominant pole for compensating the loop. The second reason to have a capacitor on the output is to help the LDO achieve its stated noise performance and both output noise voltage and power supply rejection ratio (PSRR). Due to the large capacitance value, in the order of multiple micro-farads, this output capacitor cannot be integrated and aspects such as board area, cost, and non-idealities due to soldering points, degrade the performance of the LDO. An alternative solution is to implement a capacitor-less (capless) LDO in which the dominant pole is created internally, eliminating the large output capacitor. This reduces the bill of material and area cost. A superior architecture is required to achieve high-performance, such as stability, low noise, high PSRR, and fast transient response, when designing capless LDOs.

Vidatronic’s Power Quencher® LDO technology can be integrated onto the die and does not require an output capacitor. It is designed for unconditional loop stability across a wide range of output capacitances, all the way down to zero, and will still achieve the required noise rejection all with extremely low power-consumption. Vidatronic IP blocks are available in the process nodes typical for ASIC/SoC development and therefore can be implemented on the ASIC/SoC die to supply all of the various internal power voltages necessary.

DC-DC Converters

An important figure of merit in power management units is the power efficiency, which is defined as the ratio between the total output power over the total power input to the regulator. Assuming you have a low-power LDO, its best-case efficiency can be calculated by the output voltage over the input voltage. The input voltage is inversely proportional to its drop-off voltage. Since a minimum drop-off is required for proper loop operation, LDOs have degraded efficiency.

A high-performance PMU often implements a combination of DC-DC converters and LDOs to drastically improve the efficiency. The drawback to a DC-DC converter is the introduction of switching mode blocks, which can produce switching noise in its output voltage. Extremely noise-sensitive circuits should not be supplied by DC-DC converters. One possible solution to overcome this is to cascade a DC-DC converter for efficient voltage drop followed by an LDO to clean up the supply noise. Additionally, the LDO can be bypassed according to the load requirements, avoiding efficiency degradation.

There are two types of DC-DC converter technologies: standard inductor-based DC-DC converters, which require an external inductor and capacitor to create the DC output level, and switched-capacitor DC-DC converters, which can be implemented with on-die capacitors but cannot supply as much current as inductor-based solutions. Vidatronic has both types of technologies available as silicon-proven IP.

Additionally, DC-DC converters can be used in the following modes:

- Buck mode: where the output voltage is lower than the input voltage

- Boost mode: where the output voltage is higher than the input voltage

- Bypass mode: where the input voltage is supplied directly to the output

- Combination mode: automatically supplies the correct output voltage regardless of the input voltage

Buck-boost mode is particularly common in battery-powered applications. When the battery is connected to a charger or is fully charged, the battery voltage may be higher than the required voltage of the load circuitry. Then as the battery becomes discharged, the battery voltage is lower than the required voltage of the load circuitry.

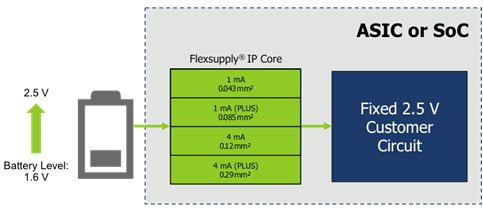

Vidatronic offers a switched capacitor DC-DC converter IP block called Flexsupply® that does not require any external components. It can generate the required output voltage regardless of whether the input voltage is above or below the required output voltage.

Figure 5: Flexsupply® DC-DC Converter Application

This IP block is designed to be scalable based on the required output current (see Figure 5). For example, if your ASIC/SoC is only going to draw 1 milliamp from the buck-boost converter, then you can use our smallest-size IP module on the die. If you were to require a higher load current, then the size of the module can scale up linearly to support the additional load. For example, a 10-milliamp load would require an area 10x the size of the area as the 1 milliamp module. This means that in your lighter-load applications, you will not pay a die-area penalty for current that you're not using.

Voltage References

Voltage references are a necessary part of the power management system in nearly any ASIC/SoC device. Voltage references are commonly used as a reference for various PMU blocks such as LDOs, op amps, comparators, data converters, and many other analog and mixed-signal functions. The main purpose of a voltage reference is to provide a constant voltage over process, voltage, and temperature (PVT) variation. Additionally, low power consumption and good power supply rejection ratio (PSRR) are part of a high-performance and reliable reference voltage. Vidatronic has a high-accuracy voltage reference IP technology that can achieve an impressive 0.3% accuracy (trimmed) with less than 10 microamps (µA) of quiescent current (IQ) and more than 80 dB of PSRR. We also have extremely low power (IQ < 100 nA) voltage references, suitable for always-on micro-power applications, with very good accuracy and noise performance. Both voltage reference families offer these high-performance benefits without using any external components.

Battery chargers

Devices such as cellphones, tablets, notebooks, smart watches, hearing aids, etc. are powered by batteries for portability. These battery-powered applications require a charger block to monitor and charge the battery cells.

Battery chargers are designed based on the battery cell requirements. Similar to voltage regulators, battery chargers can be designed as linear or switching chargers. Linear battery chargers are simple and provide a small solution size since they do not require large external components such as inductors. These kinds of battery chargers are lower cost and are suitable for small battery cells and low-power charging applications such as wearables or IoT. On the other hand, switching chargers are more suitable for high-power applications in which a larger amount of current is used to charge the battery cells for fast charging. These kinds of battery chargers can be found in cellphones, notebooks, and automotive applications.

Security Blocks

There are many other foundational analog circuit blocks that are commonly used in power management applications. These include oscillators, voltage monitors, temperature sensors, and power-on reset (POR) circuits.

Although there are many ways to implement oscillators, power management functions generally use either the relaxation or the ring architecture. While neither are novel, implementing them to reliably start and oscillate at the correct frequency across process, voltage, and temperature (PVT), with reasonable power consumption, can be challenging in advanced fab processes.

Voltage monitors and temperature sensors are frequently used for failsafe reasons, flagging the controller to shut down the system when a limit has been reached. Key parameters are accuracy and hysteresis.

Power-on reset (POR) circuits are usually a necessary part of any ASIC/SoC design, to hold off the start-up of logic circuits until the power supply voltages have reached an adequate level to achieve valid logic states in the system.

Power Management Unit (PMU)

The use of these various power management blocks on an ASIC/SoC is generally not independent. Frequently, systems require very carefully controlled power-up and power-down sequencing of the various supply rails and the ability to shut down certain power supplies during specified low-power operating states of the ASIC/SoC. To control the various power management blocks, a logic state machine is typically added to ensure the right timing and sequencing of power supply bring-up and shutdown as well as to establish the various low-power states. This logic state machine is often controlled by a microcontroller or microprocessor through a serial interface (e.g. I2C). The careful development and testing of these logic circuits and their interface with the analog power management blocks is not trivial.

Vidatronic has these various silicon-proven technologies available and has many years of experience in the appropriate implementation. Grouping these various power management blocks together with some control circuitry and an interface for external control is referred to as a power management unit (PMU). One of the customization services that Vidatronic offers is the integration of various power management blocks into a single PMU that provides all of the necessary power functions for your entire SoC design.

Conclusion/Summary

Utilizing Vidatronic IP and custom circuitry for your ASIC/SoC development can help get you to market faster, with differentiated product features and performance. Our experience reduces your overall project risk.

Vidatronic IP cores for ASIC/SoC integration include:

- LDOs that can be integrated on-die and do not require any external components

- DC-DC converters with die area scalable to the load requirement

- Voltage references featuring impressive accuracy or incredibly low power for always-on applications, without requiring external components

- Foundational security blocks

- Control logic and serial interfaces

At Vidatronic we also provide the flexibility to customize any IP block to meet specific application requirements, and integration of the required blocks together into a full PMU that provides all of the necessary power functions for your entire ASIC/SoC design.

Vidatronic specializes in the most advanced-process nodes in CMOS Planar, FinFET, and SOI technologies, from 180 nm down to 5 nm.

We are not a component vendor – our strength is in partnership. Collaboration is the key to our Partners’ success, and it allows us to grow with you in parallel. Partnering with Vidatronic can free up your valuable design engineering resources to focus on those areas where they have the most expertise so that you can develop a successful SoC that has significant value in the market, in the fastest and most cost-effective way.

Important Notices / Disclaimers

Vidatronic may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights. For a full list of Vidatronic patents, please visit our website: http://www.vidatronic.com/patents/

Vidatronic does not warrant or represent that any license, either expressed or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which Vidatronic products or services are used. Information published by Vidatronic regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property rights of the third party.

Vidatronic products are not designed, intended, or authorized for use in medical systems or in other applications intended to support or sustain life, or in any other application in which the failure of the Vidatronic product could create a situation where personal injury or death may occur. Should Buyer purchase or use Vidatronic products for any such unintended or unauthorized application, Buyer shall indemnify and hold Vidatronic and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, costs, damage and expenses and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Vidatronic was negligent regarding the design or manufacture of the product.

While the information presented herein has been checked for both accuracy and reliability, Vidatronic assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use.

Vidatronic and its subsidiaries reserve the right to make corrections, enhancement, improvements and other changes to its semiconductor products, services, data sheets and marketing materials at any time without notice. It furthermore reserves the right to discontinue any product or service.

Vidatronic warrants performance of its products and services to the specifications applicable at the time of sale, in accordance with Vidatronic’s standard warranty.

Vidatronic assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using Vidatronic products and services. To minimize the risks with customer products and applications, customers should provide adequate design and operating safeguards.

Reproductions of Vidatronic information in Product Briefs or Data Sheets is permissible only if a) obligations / requirements per Non-Disclosure Agreements are maintained and b) reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Reproduction of this information with alterations is an unfair and deceptive business practice. Vidatronic is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of Vidatronic products or services with statements different from or beyond the parameters stated by Vidatronic for that product or service voids all express and any implied warranties for the associated Vidatronic product or service and is an unfair and deceptive business practice. Vidatronic is not responsible for any such statements.

“Vidatronic”, “Innovation to Power”, “Noise Quencher”, “Power Quencher”, “Flexsupply”, “FlexPA”, and “ACCUREF” whether in word mark or design mark form, are the property of Vidatronic. For a full list of Vidatronic trademarks, please visit our website: http://www.vidatronic.com/legal/. All other referenced brands, product names, service marks and trademarks are the property of their respective owners.