D&R Industry Articles (January 2010)

Articles for the Week of January 25, 2010

A Recipe for Verification IP - The Role of Methodology

This paper will emphasize how a recipe that combines methodologies provides a superior VIP, one that reduces effort and debugging time. While avoiding reference to specific EDA tools when possible, the article also describes the creation of VIP flow at a conceptual level.- Using SerDes in Fourth Generation Wireless Infrastructure

- A nuts and bolts engineering approach to using open source IP

- Design for diagnosis to improve IC yield

- Early verification cuts design time and cost in algorithm-intensive systems

Articles for the Week of January 18, 2010

Additional Articles- Methodology for Rapid Development of Loosely Timed and Approximately Timed TLM Peripherals

- EDA from "soft business to competitive business"

- Using an FPGA to tame the power beast in consumer handheld MPUs

Articles for the Week of January 11, 2010

Architecture Oriented C Optimizations

Know your hardware! That’s what it’s all about. Using programming guidelines derived from the processor’s architecture can dramatically improve performance of C applications. In some cases, it can even make the difference between having the application implemented in C and having it implemented in assembly. Well written C code and an advanced compiler that utilizes various architectural features often reach performance results similar to those of hand written assembly code.- Deterministic dynamic memory allocation & fragmentation in C & C++

- A new approach to improving system performance

- Low power LDPC decoder created using high level synthesis

- Power Supply Design Considerations for Modern FPGAs

- A real solution for mixed signal SoC verification

Articles for the Week of January 4, 2010

A 66-mW 3.4Gbps Transmitter PHY for HDMI Applications in 2.5V 40-nm CMOS

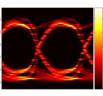

This paper presents a low-power Synopsys® DesignWare® High Definition Multimedia Interface Transmitter (HDMI TX) PHY in a 2.5V 40-nm CMOS process. It employs a number of features for IP portability and ultra-low power consumption. The DesignWare HDMI TX IP includes a half-rate serializer, a low-power PLL and clocking scheme in addition to a novel TX architecture. The architecture is portable into both 2.5V and 1.8V process nodes, and makes use of a “supply-less” termination scheme that eliminates the need for a 3.3V supply.- Low power design is here to stay

- What next for microcontrollers?

- Using OVM to reuse vital verification knowledge

- Viewpoint: Need to move beyond the network-on-chip

- Multicore technologies and software challenges

- Executive Opinion: Successful Memory IP Development Depends on GEP

- Legal compliance and open source software

- How do you qualify netlist reduction and circuit extraction?