D&R Industry Articles (September 2013)

Articles for the Week of September 30, 2013

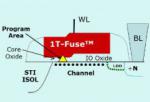

Using Sidense 1T-OTP in Power-Sensitive Applications

There are alternatives to putting an OTP on-chip. The data can be held off-chip in some sort of programmable memory (or, perhaps, ROM). But this obviously has the disadvantage of requiring the cost of an extra chip. In smartphones it is not just the cost of another chip that is a problem, but the additional volume taken up by two chips. There is just not a lot of room inside a smartphone to fit everything.Articles for the Week of September 23, 2013

A Novel Methodology to Design and Verify companion SoCs in a single package

Growing complexity of System-on-Chips (SoCs), functional debug of the additional hardware becomes a greater challenge. There may be multiple SoCs with common interface present in the same package. With evolution of these complex architecture, need arises not only for design innovation but also for verification strategy which can help verify such design quickly and effectively. This paper discuss about the need to have such design and its efficient verification methodology.- The future of Android in vehicles

- Safety & security architecture for automotive ICs

- How Reusable IP Helps Reduce Product Design Cycles

- Tips for doing effective hardware/firmware codesign: Part 2

Articles for the Week of September 16, 2013

An efficient approach to evaluate Dynamic and Static voltage-drop on a multi-million transistor SoC design

This paper describes the methodology and technology we used, to assess full-chip dynamic and static IR-drop for such complex and huge SoCs. Firstly, it outlines power-grid weakness and hot spot exploration using a testcase of STB SoC in 65nm WireBond and Flipchip variants. Additionally, it outlines the complexity in performing voltage drop analysis in vector-less mode without a VCD in terms of methodology and technology, specifically due to flipchip complexity.- Building more secure embedded software with code coverage analysis

- Verification care abouts for SoC internal channel characterization using an ADC

- Digital Signal Processing (DSP) Verification

Articles for the Week of September 9, 2013

Easier UVM Sequences - SystemVerilog UVM Sequence and Task Equivalence

SystemVerilog UVM sequences are a powerful way to model stimulus and response for functional verification. Unfortunately using SystemVerilog UVM sequences can require an extensive background in SystemVerilog, the UVM and object oriented programming. This paper explains a collection of techniques to allow the power of sequences with familiarity and simplicity of calling tasks.Articles for the Week of September 2, 2013

Additional Articles- Tips for doing effective hardware/firmware codesign

- Selecting the right RTOS scheduling algorithms using system modelling