D&R Industry Articles (June 2017)

Articles for the Week of June 26, 2017

Addressing SRAM Verification Challenges

Verification is an integral part of any integrated circuit development process. The verification process must establish that the design meets its specified yield and performance criteria over the full range of operating conditions before tape-out sign-off. The process generally involves taking abstractions of the design in appropriate forms, for example post-layout extracted netlists, and running simulations to validate the design performance. The verification process must address many different aspects of yield and performance, so several different types of design abstraction and simulation tooling may be required to complete the process. In the case of SRAM this is particularly true.- Power Optimization using Multi BIT flops and MIMCAPs in 16nm technology and below

- Achieving FPGA Design Performance Quickly

Articles for the Week of June 19, 2017

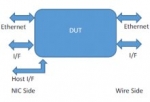

QEMU based Co-simulation platform - Benefits

This paper proposes a flow which illustrates how to develop and test software early in the development phase along with design-verification cycle. Also this paper highlights the benefits of the flow which will not only reduce the development cycle but also improve the quality of product.Articles for the Week of June 12, 2017

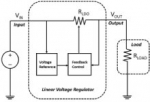

Introduction to Low Dropout (LDO) Linear Voltage Regulators

Linear voltage regulators are key components in any power-management system that requires a stable and ripple-free power supply. A subset of linear voltage regulators is a class of circuits known as low dropout (LDO) regulators. This paper explains the fundamentals of LDOs and introduces Vidatronic’s LDO technology which solves many of the known shortcomings of LDO circuits.- Communication Processors March on But 5G Demands Much More

- Randsequence: SystemVerilog's unsung hero