Featured Article

Allowing battery-powered devices to run, without battery recharge, for years rather than months, partakes in enhancing significantly end-user satisfaction and is a key point to enabling the emergence of IoT applications. Numerous applications, such as M2M, BLE, Zigbee…, have an activity rate (duty cycle) such that the power consumption in sleep mode dominates the overall current drawn by the SoC (System on Chip). For such applications, the design of the “Always-On power domain" (a.k.a AON power domain) is pivotal.

Featured Article

Here we provide rational for using Centar’s floating-point IP core for the new Altera Arria 10 and Stratix 10 FPGA platforms. After a short contextual discussion section, a comparison of various FFT designs follows based on compilations to a couple of FPGAs. Here it is shown that LUT/register usage can be drastically reduced with this new class of FPGAs. The following section summarizes why Centar’s architecture is so effective in taking advantage of the new DSP block hardware.

Featured Article

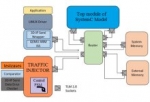

As the system, software & IP complexity is increasing so is the demand of SystemC models & Virtual Platform for verification. To achieve it, the key requirements are that the models/platform should be developed fast, reusable & highly accurate. We are sharing the experience of our company 3D-IP Semiconductors Ltd. for the development of a generic Virtual Platform using TLM 2.0; reusable for any system model.