Performance analysis of 8-bit pipelined Asynchronous Processor core

By Yasha Jyothi M Shirur, Veena S Chakravarthi, Gourav Thakur (BNM Institute of Technology)

Abstract

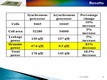

Today’s complex VLSI SOC solutions demand low power processors. Synchronous processors which consume more than 40 % of power in clock circuitry are being conveniently replaced by low power delay-insensitive (DI) asynchronous Processor modules/cores. In this paper, power, area performance parameters of 8-bit pipelined asynchronous processor is measured and compared over similar feature synchronous processor. The Asynchronous processor supports 28 Arithmetic and Logical Instructions. The module to module hand shaking is performed using 2 phase mousetrap pipelining. The implemented processor has given dynamic power advantage of 49% over synchronous processor. The design is a synthesizable core which can be extended to complex RISC or DSP architectures by integrating MAC (Multiplier and Accumulator) core and hence is a right choice for any MPSOC designs.