RT-260 Compact Root of Trust for IoT with DPA, IIoT and cloud-connected devices, sensors, gateways

Scalable Architectures for Analog IP on Advanced Process Nodes

By Manuel Mota (Synopsys)

Abstract

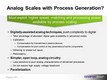

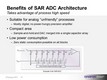

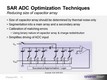

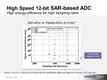

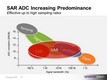

Design teams tackling mixed-signal system-on-chip (SoC) designs face the problem of how to get the most out of advanced process technologies when it comes to implementing their analog IP. They need to take a different approach to mixed-signal design and utilize analog architectures that better suit the latest digital process technologies. Applications that typically depend on mixed-signal SoCs include mobile communications, wireless applications and multimedia devices, such as set-top boxes and digital TVs. They need to take analog signals from radio transmitters, wireline transceivers and sensors. One of the key tasks for mixed-signal SoCs is to convert the incoming analog signal to a digital signal for processing on the chip using an accurate analog-to-digital converter, or ADC. According to Moore’s Law, SoC density is expected to increase by 1.5X-2X in every new process generation, and power consumption must reduce by the same factor.. However, analog components cannot immediately take advantage of feature size reductions. In fact, dynamic range and accuracy requirements limit area and power consumption irrespective of process improvements. To achieve scaling factors similar to digital circuits, analog circuits must exploit the higher speed and processing power made available by Moore’s Law scaling. For example, more compact analog blocks can perform the same functions of more complex ones by relying on digital compensation, calibration, and higher processing speed, leading to the concept of digitally enabled analog circuits. This paper elaborates on how ADCs can work with Moore's Law to move with the power and area scaling trends that are common for digital circuits. It will: • Compare the main ADC architectures and conclude that the Successive-Approximation Register (SAR) based ADC is very well positioned as the architecture of choice for medium- and high-speed ADCs in modern SoCs, especially in 28-nm processes and beyond. • Describe implementations of the SAR ADC architecture that reduce power consumption and area usage dramatically, enabling SoC designers to successfully integrate these analog components in their next SoCs.