A Clock Tree Synthesis Flow Tailored for Low Power

By Arzu Datli, Umut Eksi, Gokhan Isik (Ericsson)

Abstract

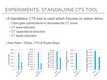

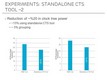

This paper aims to share practical experience regarding building a power-optimized clock tree, determining the optimum targets for clock tree synthesis (CTS) and monitoring the quality of results (QoR) along the way. The experiments that will be presented were conducted on a mixed-mode design, which has multiple power domains with 100K+ registers, and which was intended for a 55nm CMOS technology node. The methodology presented here resulted in clock tree power savings of up to 20% according to simulation results.