Evatronix Adds the Scaling Capabilities to its PANTA DP20 Display Processor

Update: Cadence Completes Acquisition of Evatronix IP Business (Jun 13, 2013)

The configurable PANTA CP10 coprocessor enables high-quality real-time 2D image up- and down-scaling within the PANTA DP20 design.Bielsko-Biala/Poland, January 28th, 2013 - Silicon intellectual property (IP) provider Evatronix SA has announced the new version of the advanced display processor, PANTA DP20, which now features scaling capabilities provided by a separate, yet easily integrable PANTA CP10 coprocessor. Utilizing latest ARM technology like TrustZone and AXI4 the PANTA DP20 is targeted specifically at high-end mobile/portable products, like smartphones and tablets, with ultra-low power consumption and impressive processing performance.

PANTA CP10 Demontration Video

There are two scaling algorithms implemented in the PANTA CP10 so that user can choose the best one for his application. For both methods there are plenty of configurable parameters that can further optimize the scaling process.

The main scaling algorithm in the PANTA CP10 is based on polyphase multi-tap filtering, and utilizes 6-tap and 16-phase filters. Input and output resolutions are register programmable in the design together with a set of filter coefficients.

EXAMPLE APPLICATION

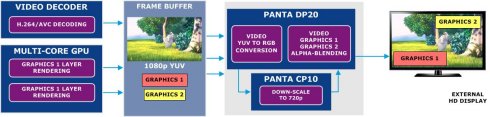

An example application is a graphics subsystem which utilizes the PANTA DP20 display processor equipped with the PANTA CP10 scaling coprocessor. In this case the GPU is responsible only for rendering graphics layer pixels and sending them to the frame buffer, being reliefed from the following operations: YUV to RGB conversion, alpha-blending and scaling. These are now handled by the PANTA DP20 and CP10 units in the most efficient way.

In the presented system, the video layer converted by the PANTA DP20 to the RGB format is composed with the other graphics layers and directly displayed on the external panel. At the same time the composed frame is down-scaled from 1080p to 720p by the PANTA CP10 module and forwarded directly to the composition module of the DP20 IP. Thanks to the PANTA CP10 scaling capability this power-consuming operation is not executed in the GPU and therefore the overall SoC power consumption significantly decreases.

Total power consumption of PANTA components presented in this use case and implemented in the 40nm LP process is less than 30 mW.

ABOUT THE EVATRONIX PANTA FAMILY

Evatronix PANTA is a family of high-resolution display controller and processor IP cores for advanced multimedia applications. Developed as a result of a strategic partnership with ARM, these cores feature the latest technologies available for mobile devices, thus enabling creation of revolutionary applications and greatly enhanced user experience.

ABOUT EVATRONIX

Evatronix develops digital and mixed-signal IP cores with complementary software and supporting application environments. The company embraces hardware, software and design service elements to assist its customers in all SoC development stages, from concept to tape-out. Over a period of more than 20 years, Evatronix has provided over 500 licenses for 8051, USB, NAND Flash, SDIO and multimedia solutions. Headquartered in Poland, Evatronix employs more than 90 people worldwide.

For more information please visit the company's web site at www.evatronix.com/ip

|

||||||

Related News

- Evatronix to Demonstrate the PANTA DP30 Display Processor Prototype at the ARM TechCon 2012

- Evatronix Launches Display Processor based on Latest ARM Security Technology

- StarFive's RISC-V based JH-7110 intelligent vision processing platform adopted VeriSilicon's Display Processor IP

- Elevate Your Display and Camera SOC Capabilities with our latest Silicon Proven MIPI C-D Combo Tx/Rx PHY and DSI Controller IP Cores

- Socionext to Showcase Leading-Edge Technologies at CES 2024, Featuring Custom SoC Solutions, Low Power Sensors, Smart Display Controller, and Advanced Image Processor

Breaking News

- JEDEC® and Industry Leaders Collaborate to Release JESD270-4 HBM4 Standard: Advancing Bandwidth, Efficiency, and Capacity for AI and HPC

- BrainChip Gives the Edge to Search and Rescue Operations

- ASML targeted in latest round of US tariffs

- Andes Technology Celebrates 20 Years with New Logo and Headquarters Expansion

- Creonic Unveils Bold Rebrand to Drive Innovation in Communication Technologies

Most Popular

- Cadence to Acquire Arm Artisan Foundation IP Business

- AMD Achieves First TSMC N2 Product Silicon Milestone

- Why Do Hyperscalers Design Their Own CPUs?

- Siemens to accelerate customer time to market with advanced silicon IP through new Alphawave Semi partnership

- New TSN-MACsec IP core for secure data transmission in 5G/6G communication networks

|

|

E-mail This Article |

|

Printer-Friendly Page |