Munich, Germany – June 2nd, 2020 – Codasip GmbH, the leading supplier of configurable RISC-V® embedded processor IP, announced today that the Codasip SweRV Support Package has been extended to include the open source, RISC-V-based SweRV Core™ EH2 and EL2 that were contributed to CHIPS Alliance by Western Digital. These have been added to the support already released for the SweRV Core EH1.

The SweRV cores EH2 and EL2 are available to the open-source community through CHIPS Alliance, an open-source development organization which seeks to provide a barrier-free environment to allow collaboration for open-source software and hardware code. The rapid inclusion of EH2 and EL2 in the Codasip SweRV Support Package after their release by CHIPS Alliance was enabled by the close cooperation of Codasip and Western Digital RISC-V teams.

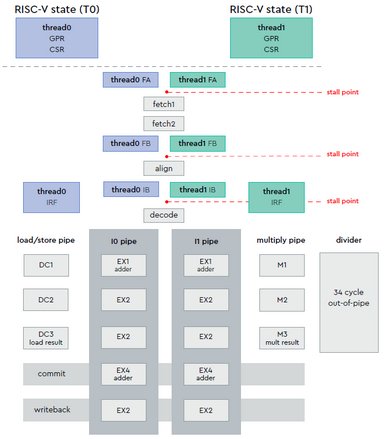

The SweRV Core EH2 is a high-performance 32-bit, dual-thread, superscalar, 9-stage pipeline core with simulated performance of up to 6.3 CoreMark/MHz and a footprint of 0.067 mm2 TSMC’s 16nm CMOS process technology. The core supports the RISC-V RV32IMAC instruction set plus bit manipulation extensions.

SweRV Core™ EH2 by Western Digital

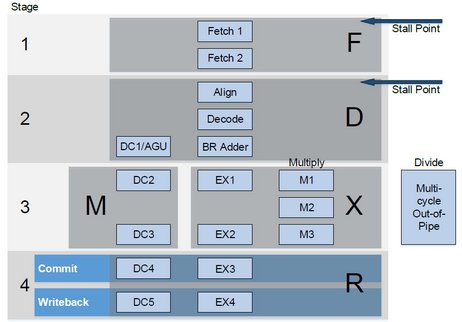

The SweRV Core EL2 is a second-generation SweRV core aimed at medium-performance embedded applications. It is a 32-bit, single issue with a 4-stage pipeline with simulated performance of 3.6 CoreMark/MHz and supporting the RISC-V RV32IMC instruction set.

SweRV Core™ EL2 by Western Digital

“We are excited to release support for Western Digital’s SweRV EH2 and EL2 cores made available through CHIPS Alliance,” noted Přemysl Václavík, Senior Director Open IP, Codasip. “The dual thread SweRV EH2 delivers outstanding embedded performance and the EL2 great silicon efficiency. Our SweRV Support Package will enable their rapid adoption in the market. We look forward to this solution helping to accelerate the RISC-V ecosystem.”

The SweRV Support Package, developed by Codasip in cooperation with Western Digital, provides a comprehensive set of tools and components needed to design, implement, test, and write software for a SweRV Core-based system-on-chip, integrated into one smart ready-to-use working environment. The Free version aimed at the educational market contains support for the software toolchain, open-source EDA tools, design flow integration, and a user forum. The Pro version additionally provides support for commercial EDA flows and professional customer support.