ICE-IP-338 High-speed XTS-GCM Multi Stream Inline Cipher Engine

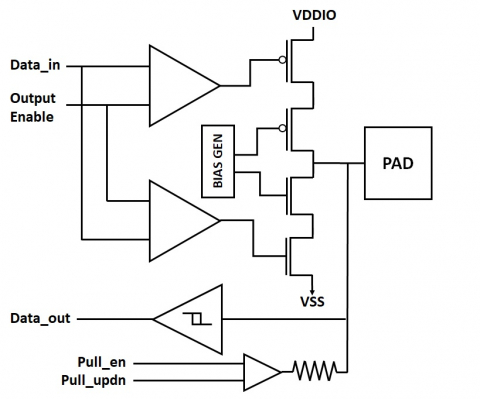

1.8V/3.3V Switchable GPIO With 3.3V I2C Open Drain & Analog in 22nm

View 1.8V/3.3V Switchable GPIO With 3.3V I2C Open Drain & Analog in 22nm full description to...

- see the entire 1.8V/3.3V Switchable GPIO With 3.3V I2C Open Drain & Analog in 22nm datasheet

- get in contact with 1.8V/3.3V Switchable GPIO With 3.3V I2C Open Drain & Analog in 22nm Supplier

Block Diagram of the 1.8V/3.3V Switchable GPIO With 3.3V I2C Open Drain & Analog in 22nm