Ceva-Waves Bluetooth 5.3 Low Energy Baseband Controller, software and profiles

10-bit, 100KS/s ULP SAR ADC

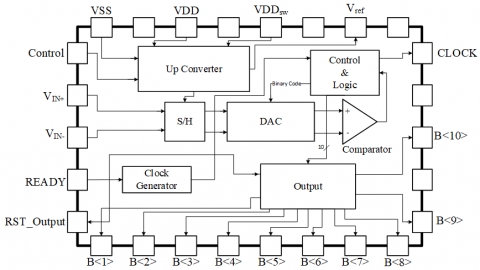

The ADC contains a clock generator block and there is no need of external clock signal. READY signal is the external sampling signal and controls the conversion procedure. Sampling block requires 1.2 V voltage signal to drive its switches. The converter block can generate this voltage internally or an external supply (VDDsw pin) can feed the sampling block.

SAR architecture is employed in this ADC in order to use the benefits of technology shrinking. In other words, size and power consumption of the block can be reduced by technology scaling in this structure.

View 10-bit, 100KS/s ULP SAR ADC full description to...

- see the entire 10-bit, 100KS/s ULP SAR ADC datasheet

- get in contact with 10-bit, 100KS/s ULP SAR ADC Supplier

Block Diagram of the 10-bit, 100KS/s ULP SAR ADC

Ultra-low power IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-100 ultra-low power 32-bit RISC-V processor for embedded applications

- GNSS (GPS, Galileo, GLONASS, Beidou3, QZSS, SBAS) Ultra-low power RF Receiver IP

- Ultra-low power 32 kHz RC oscillator designed in GlobalFoundries 22FDX

- 8-Channel Ultra-Low Power Capacitive Touch Interface

- Compact ARC EM Processors feature excellent code density, small size, and ultra-low power consumption for power-sensitive, area-critical embedded applications