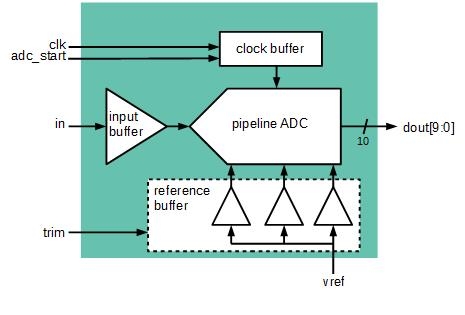

10 Bit 40 MS/s Pipeline ADC

The latency of the ADC is 10 clock cycles. On the one hand, the ADC operation can be triggered using the adc_start input signal. On the other hand, continuous conversion of the input signal can be selected.

The integrated buffer provides a high impedance input in order to simplify the interface to the driving circuit. For low-power consumption a sample-and-hold-less architecture is used.

The reference drivers are included, which enables the operation using a single reference voltage. 7 bit trimming of the reference is included.

The ADC is silicon proven using the AMS H18 process. Measurement results are available from evaluation and volume production. One application of the IP is an industrial sensor ASIC for safety critical applications.

Fraunhofer IIS provides a detailed documentation and support for the IP integration. Modifications, extensions and technology ports of the IP are available on request.

View 10 Bit 40 MS/s Pipeline ADC full description to...

- see the entire 10 Bit 40 MS/s Pipeline ADC datasheet

- get in contact with 10 Bit 40 MS/s Pipeline ADC Supplier

Block Diagram of the 10 Bit 40 MS/s Pipeline ADC IP Core