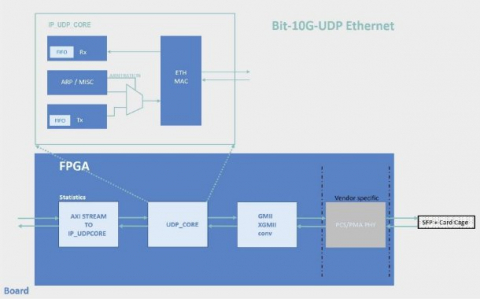

10 Gb/s full HW stack UDP/IP Transmitter/Receiver

In application areas such as Data Communication and Imaging, there is a need for increased transfer speeds to handle higher resolutions and higher acquisition rates. This implies more complex solutions in terms of FPGA and board design. This IP core is a real-time offload engine where the communication is processed and accelerated in HW – all the way from UDP to Ethernet Phy. An Ethernet PHY can be integrated in the FPGA enabling a direct connect to the fiber optical SFP+ transceiver.

With data transfer near line rate at theoretical maximum throughput, it is useful for sending large amount of data to a remote PC or host.

View 10 Gb/s full HW stack UDP/IP Transmitter/Receiver full description to...

- see the entire 10 Gb/s full HW stack UDP/IP Transmitter/Receiver datasheet

- get in contact with 10 Gb/s full HW stack UDP/IP Transmitter/Receiver Supplier

Block Diagram of the 10 Gb/s full HW stack UDP/IP Transmitter/Receiver