10Gb Ethernet XGXS

The ORT82G5 is a high-speed transceiver with an aggregate bandwidth of up to 29.6 Gbits/s that is targeted towards users in need of high-speed backplane and chip-to-chip interfaces using Ethernet and Fibre-Channel based protocols. The ORT82G5 has eight channels of integrated 0.6-3.7 Gbits/s SERDES channels that can be used as 2x10 Gbits/s XAUI interfaces.

XAUI is a high-speed interconnect that offers reduced pin count and is specified to drive up to 20 inches of PCB trace on standard FR-4 material. Each XAUI interface comprises four self-timed 8b/10b encoded serial lanes each operating at 3.125 Gbits/s and thus is capable of transferring data at an aggregate rate of 10 Gbits/s.

XGMII is a 156MHz Double Data Rate (DDR), parallel, short-reach interconnect interface (typically less than two inches). It supports interfacing to 10Gb/s Ethernet Media Access Control (MAC) and PHY devices.

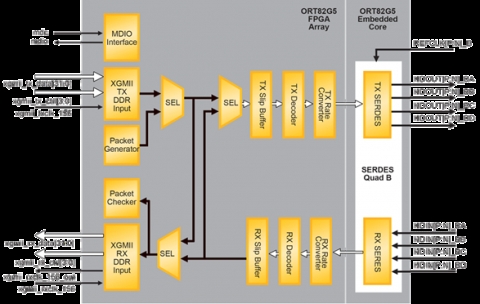

In this design, the XGXS core is implemented in the FPGA portion of the device. A packet generator/checker and MDIO interface are also implemented in the FPGA logic.

The XGXS IP core is provided with implementation scripts, test benches, and documentation to allow users to integrate the functions for 10 GbE LAN/WAN applications.

View 10Gb Ethernet XGXS full description to...

- see the entire 10Gb Ethernet XGXS datasheet

- get in contact with 10Gb Ethernet XGXS Supplier

Block Diagram of the 10Gb Ethernet XGXS IP Core

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software