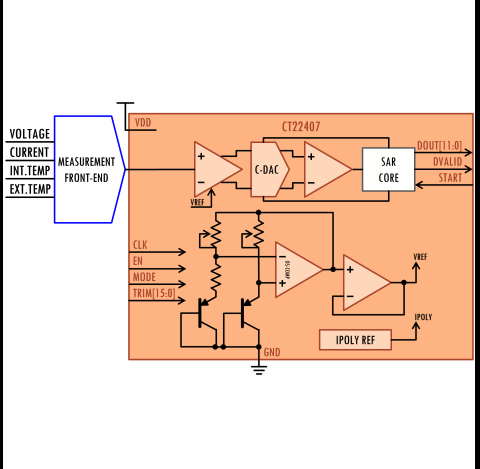

12 Bits, 100 kS/s SAR Analog to Digital Converter

The core of the IP is a 12-bit Capacitive Charge-Redistribution SAR ADC converting the analog measurement into the digital domain.

Its reference voltage VREF is generated internally, buffering an internally generated bandgap voltage.

Due to the fully-differential architecture of the analog front end, measuring voltage requires a single ended to fully differential conversion through included switched cap amplifier that acts also as a sample and hold and performs the required gain adjustment to properly condition the signal for the SAR ADC Core.

Due to the high accuracy requirements, accurate single temperature trimming of the internal reference voltage has to be performed.

Input voltage range is assumed to be 0÷1.8V.

Programmable measurement averaging can be performed and therefore output can be set as the result of a single conversion or the average of 2/4/8 conversions.

View 12 Bits, 100 kS/s SAR Analog to Digital Converter full description to...

- see the entire 12 Bits, 100 kS/s SAR Analog to Digital Converter datasheet

- get in contact with 12 Bits, 100 kS/s SAR Analog to Digital Converter Supplier

Block Diagram of the 12 Bits, 100 kS/s SAR Analog to Digital Converter

SAR; ULP; Low; Power; ADC; IP

- 12bit 160Msps Ultra low power SAR ADC IP Core

- ULP 12 Bits, 35 kS/s SAR Analog to Digital Converter

- Narrow band - IoT Ultra-Low power UE RF Transceiver IP

- Low Power 12bit 640Msps silicon proven High performance Current Steering DAC IP Core

- GNSS (GPS, Galileo, GLONASS, Beidou3, QZSS, SBAS) Ultra-low power RF Receiver IP

- Dual channel 12-bit, 640MS/s ADC IP for WIFI6 in TSMC 22nm