DDR2/DDR3/DDR3L/LPDDR/LPDDR2/LPDDR3 6 in one combo IO with auto calibration - 40nm LL

16 bit DSP fixed point coprocessor

The IP is available in a variety of formats, FPGA netlist for both production and verification, soft core and as source code ensuring ease of integration and maximum control of synthesis choices.

We understand that the development tools are as important as the CPU itself. Multiple debug interface options are available to suit your design needs – from a simple serial port to complete JTAG. Since the tools are based on the industry standard GNU tools, GCC and GDB, these are available to you and your customers without cost or re-training.

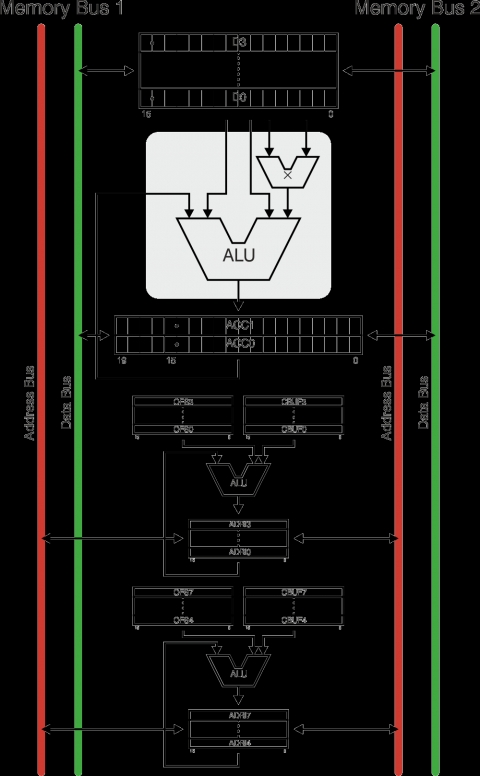

The APS DSP co-processor core is a fixed point general purpose 16 bit DSP extension to the APS5 or FPS6 processors. It extends both the instruction set and register set of the main CPU enhancing the performance of the system for numerous applications.

It provides two additional memory interfaces, ensuring the memory bandwidth necessary for demanding signal processing applications.

It has three ALUs operating in parallel, allowing one arithmetic operation and two address calculations per cycle.

The address ALUs support a number of addressing modes, implementing circular buffers and bit reverse arithmetic without additional program support. Two 32k by 32 bit memory interfaces give algorithms ample and efficient access to parameters.

The main ALU has four 16 bit general purpose registers and two 20 bit accumulators. A 16 x 16 multiplier gives 20 bit results. The address ALUs have four address pointers each associated with an offset register and circular buffer register, all of which are 16 bits long. It can be configured for either saturating or non-saturating arithmetic

The Zero Overhead Loop (zol) construct allows part of an algorithm to be iterated automatically. The instructions are stored in an internal buffer and are only required to be fetched once for the entire loop.

This loop then executes completely in parallel to the application running on the main CPU.

The Harvard bus architecture ensures simple memory design. Dual memory interfaces ensure that each instruction can perform two memory accesses as well as the instruction fetch.

See for yourself how the APS5 or FPS6 and APS DSP meet your needs with the low cost evaluation board.

View 16 bit DSP fixed point coprocessor full description to...

- see the entire 16 bit DSP fixed point coprocessor datasheet

- get in contact with 16 bit DSP fixed point coprocessor Supplier

Block Diagram of the 16 bit DSP fixed point coprocessor IP Core