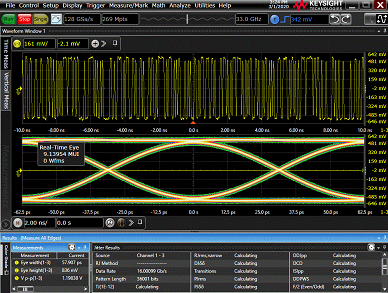

16Gbps multi-protocol programmable SerDes PHY in UMC 28HPC+

The silicon verified 16Gbps SerDes PHY supports the optimization of SoC chip designs to enable the infrastructure of 10G/40G Ethernet, PCIe 4.0, 5G, and most xPON applications. Compared with the other latest Serdes solutions, it is the only solution that supports both PCIe 4.0 and 10G xPON ONU/OLT in 28nm node.

This full-duplex, high-performance and many-protocols compatible SerDes solution comes with a scalable PMA which can be applied to a wide range of applications across copper and backplane channels with total insertion loss more than 30dB. It is also compatible with standard PCS and controller, and provides flexible design environment for users to customize PCS and controller integration.

View 16Gbps multi-protocol programmable SerDes PHY in UMC 28HPC+ full description to...

- see the entire 16Gbps multi-protocol programmable SerDes PHY in UMC 28HPC+ datasheet

- get in contact with 16Gbps multi-protocol programmable SerDes PHY in UMC 28HPC+ Supplier

Block Diagram of the 16Gbps multi-protocol programmable SerDes PHY in UMC 28HPC+

Interface Solution IP

- PCIe 6.1 Controller

- Compute Express Link (CXL) 2.0 Controller with AMBA AXI interface

- PCIe 5.0 Controller with AMBA AXI interface

- PCIe 4.0 Controller with AMBA AXI interface

- Very compact (500 LUTs) Camera Sensor Receiver Interface Converting from MIPI CSI-2 to AXI4-Stream Video Standard

- HW/SW interface foundation for design innovation