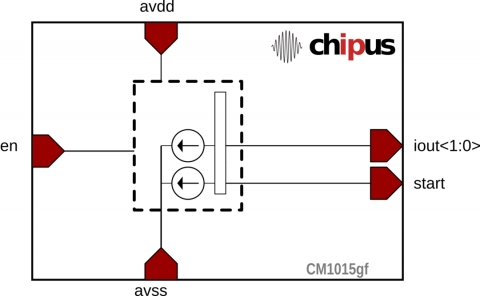

17nA Current Bias with Enable - Low Voltage (1.0V), Ultra Low Power (90nW @ 1.8V) TowerJazz 0.18 μm

The circuit generates 2 × NMOS 17nA current branches. The current bias is temperature compensated. Output currents come from NMOS drain terminals, thus being sink-type sources.

View 17nA Current Bias with Enable - Low Voltage (1.0V), Ultra Low Power (90nW @ 1.8V) TowerJazz 0.18 μm full description to...

- see the entire 17nA Current Bias with Enable - Low Voltage (1.0V), Ultra Low Power (90nW @ 1.8V) TowerJazz 0.18 μm datasheet

- get in contact with 17nA Current Bias with Enable - Low Voltage (1.0V), Ultra Low Power (90nW @ 1.8V) TowerJazz 0.18 μm Supplier

Block Diagram of the 17nA Current Bias with Enable - Low Voltage (1.0V), Ultra Low Power (90nW @ 1.8V) TowerJazz 0.18 μm