1G Unmanaged Ethernet Switch

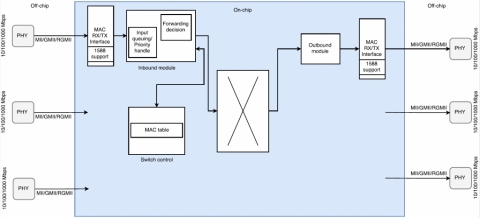

The switch implements a non-blocking crossbar matrix that allows wire-speed communication among all the ports. The switch buffers and verifi es each frame before forwarding it. Nevertheless, the latency time has been minimized to nanoseconds order. Furthermore, UES supports IEEE 1588 V2 Transparent Clock functionalities. This feature, that corrects PTP frames introducing the error generated by the switch, allows the interconnection of IEEE 1588 synchronized devices maintaining the highest levels of accuracy.

UES is the perfect Ethernet Switch IP to implement Ethernet based Industrial Networks. It provides MII/GMII/RGMII native interfaces for Ethernet PHY devices and it can be combined with Xilinx IP to support RMII or SGMII among other interfaces. It also supports and AXI4-Stream interface to be connected to other IP Cores that do not feature MAC based interfaces.

View 1G Unmanaged Ethernet Switch full description to...

- see the entire 1G Unmanaged Ethernet Switch datasheet

- get in contact with 1G Unmanaged Ethernet Switch Supplier

Block Diagram of the 1G Unmanaged Ethernet Switch IP Core

Ethernet Switch IP

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- TSN Ethernet Switch

- Multi Protocol Switch IP Core for Safe and Secure Ethernet Network

- Multi Protocol Switch IP Core for Safe and Secure Ethernet Network

- Multi Protocol Endpoint IP Core for Safe and Secure Ethernet Network

- Ethernet IPSec/MACSec Switch/Router IP Core - Efficient and Massively Customizable