2-16Gbps Multi-Protocol IO Supporting BOW, OHBI and UCIe

AresCORE16 can be configured to support advanced packaging such as CoWoS (Chip-on-Wafer-on-Substrate), InFO (Integrated-Fan-Out) for maximum density, and Organic Substrates for most cost-effective solution covering all market segments.

View 2-16Gbps Multi-Protocol IO Supporting BOW, OHBI and UCIe full description to...

- see the entire 2-16Gbps Multi-Protocol IO Supporting BOW, OHBI and UCIe datasheet

- get in contact with 2-16Gbps Multi-Protocol IO Supporting BOW, OHBI and UCIe Supplier

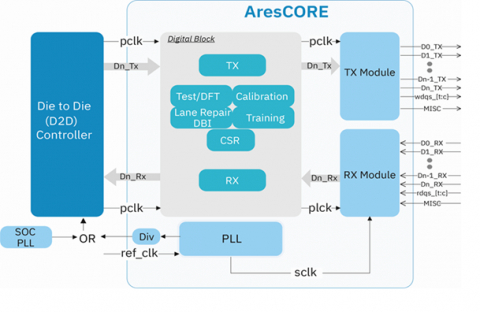

Block Diagram of the 2-16Gbps Multi-Protocol IO Supporting BOW, OHBI and UCIe

SerDes IP

- PCIe 5.0 Serdes PHY IP, Silicon Proven in TSMC 12FFC

- Low-Latency SerDes PMA - 10GbE, 25GbE

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- 400G ultra low latency 56/112G FEC and SERDES IP sub 10ns latency

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency