2.5G/1000M/100M/10M Quad-Mode MAC

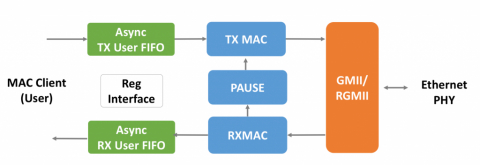

The west-bound interface from the MAC provides a configurable 32-bit system interface.

The east-bound interface performs the mapping of transmit and receive data streams (at the PHY layer) to the on-chip SERDES or external PHY chip.

View 2.5G/1000M/100M/10M Quad-Mode MAC full description to...

- see the entire 2.5G/1000M/100M/10M Quad-Mode MAC datasheet

- get in contact with 2.5G/1000M/100M/10M Quad-Mode MAC Supplier

Block Diagram of the 2.5G/1000M/100M/10M Quad-Mode MAC