2.5Gbps Ethernet PCS IP Core

The two major non-compliances are data rate (2.5 Gbps instead of 1 Gbps) and GMII data bus width (16 bits instead of 8 bits).

This PCS IP core was specifically developed to operate with the Lattice 2.5 Gbps MAC IP core. The Lattice 2.5G PCS and MAC IP cores are 100% compatible and can be used to create a full PHY/MAC Ethernet data path that operates at 2.5 Gbps.

This document describes the 2.5 Gbps Ethernet PCS IP core’s operation, and provides instructions for generating the core through the Lattice IPexpress™ tool, and for instantiating, synthesizing, and simulating the core.

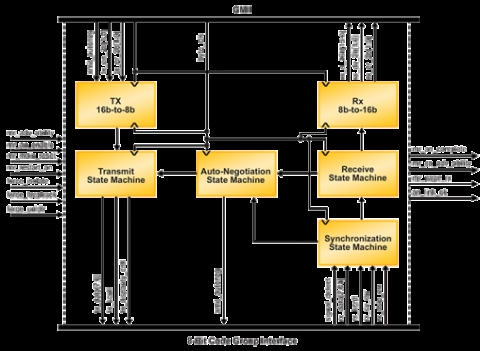

The 2.5 Gbps Ethernet PCS IP core converts GMII frames into 8-bit code groups in both transmit and receive directions and performs auto-negotiation with a link partner as described in IEEE 802.3z specification.

View 2.5Gbps Ethernet PCS IP Core full description to...

- see the entire 2.5Gbps Ethernet PCS IP Core datasheet

- get in contact with 2.5Gbps Ethernet PCS IP Core Supplier

Block Diagram of the 2.5Gbps Ethernet PCS IP Core IP Core

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software