2.5Gbps Per Lane MIPI-CSI2 Compliant Serial Video Transmitter

The SVTPlus2500 complies with MIPI CSI2 and DPHY specifications (version 2.0 of both documents).

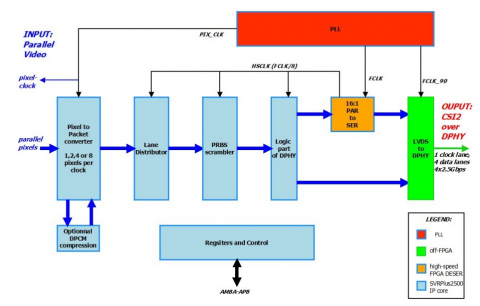

The SVTPlus2500 receives parallel pixels from a video source (1,2,4 or 8 pixels per clock). The pixels are translated to MIPI CSI2 packets and output from the SVTPlus2500 by high-speed parallel and low-power signals. The high-speed parallel signals are converted by an FPGA-specific high-speed 16:1 seriallizer, to DPHY high-speed signals, at up to 2.5Gbps per lane. An external LVDS to DPHY device converts the high speed and the low-power inputs to DPHY signals, transmitted over a single clock lane and up to four data lanes. A simple CPU is typically required for configuration and, if needed, for diagnostics.

View 2.5Gbps Per Lane MIPI-CSI2 Compliant Serial Video Transmitter full description to...

- see the entire 2.5Gbps Per Lane MIPI-CSI2 Compliant Serial Video Transmitter datasheet

- get in contact with 2.5Gbps Per Lane MIPI-CSI2 Compliant Serial Video Transmitter Supplier

Block Diagram of the 2.5Gbps Per Lane MIPI-CSI2 Compliant Serial Video Transmitter

MIPI CSI2 Transmitter IP

- MIPI CSI DSI Controller - CPHY CSI-2 Transmitter v 2.1, Compatible with MIPI C-PHY v1.2 & DPHY v2.1.

- MIPI D-PHY CSI-2 TX (Transmitter) in TSMC 28HPC+

- MIPI D-PHY CSI-2 TX+ (Transmitter) IP in TSMC 22ULL

- MIPI C-PHY/D-PHY Combo CSI-2 TX (Transmitter) in TSMC 40ULP

- MIPI D-PHY CSI-2 TX+ (Transmitter) IP in TSMC 28HPC+

- MIPI D-PHY CSI-2 TX (Transmitter) in GlobalFoundries 22FDX