25G LL MAC /PCS Ethernet IP for FPGA

Ultra-low latency is achieved on the PCS block by using only the PMA function in FPGA Multi-Gigabit transceivers and moving all PCS functions to code that is optimized for 25GBASE-R. This allows the data to take the shortest, and hence the lowest latency, path to and from the wire.

The MAC manages frame timing, CRC32 Checksum insertion and generation, and manages the lower layer fault handling and XXVGMII interface coding. Chevin Technology’s MAC/PCS is XXVGMII compatible with a 64bit interface at 390.625MHz. A detailed statistics block provides a running count of frames sent and received with individual 64bit counters for different frame sizes, types and checksum errors.

View 25G LL MAC /PCS Ethernet IP for FPGA full description to...

- see the entire 25G LL MAC /PCS Ethernet IP for FPGA datasheet

- get in contact with 25G LL MAC /PCS Ethernet IP for FPGA Supplier

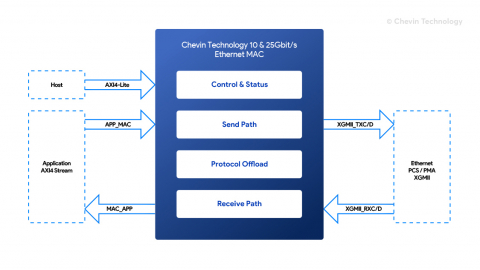

Block Diagram of the 25G LL MAC /PCS Ethernet IP for FPGA