25Gbps Ethernet and CPRI-10 FEC Layer IP Core

The IP core supports both 25GE FEC layer, 32GFC and CPRI-10 FEC layer functions. The configuration is dynamically switchable via software register.

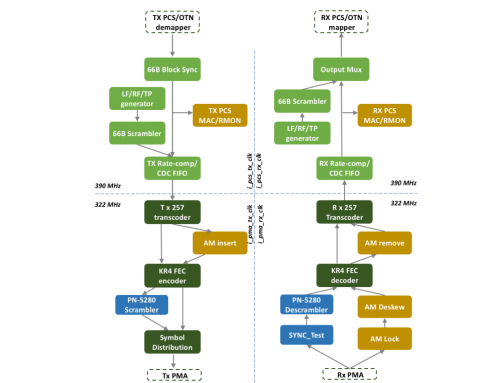

The north-bound interface from the MAC/PCS provides a 66-bit PCS interface or 66B OTN mapping layer.

The southbound interface performs the mapping of transmit and receive data streams (at the PMA layer) to the on-chip SERDES. This core is responsible for channel alignment and KR4 FEC management. The PCS supports an interface for 25GBASE-CR or 25GBASE-KR.

View 25Gbps Ethernet and CPRI-10 FEC Layer IP Core full description to...

- see the entire 25Gbps Ethernet and CPRI-10 FEC Layer IP Core datasheet

- get in contact with 25Gbps Ethernet and CPRI-10 FEC Layer IP Core Supplier

Block Diagram of the 25Gbps Ethernet and CPRI-10 FEC Layer IP Core

Ethernet IP

- 10G-100G MACsec Security Module for Ethernet

- 224G Ethernet PHY in TSMC (N3E, N2P)

- 112G Ethernet PHY in TSMC (N7, N6, N5, N3P)

- Multi-protocol SerDes PMA - PCIe1 PCIe2 PCIe3 PCIe4 PCIe5 and more

- 1-56/112G Multi-protocol Serdes (Interlaken, JESD204, CPRI, Ethernet, OIF/CEI)

- PCIe Gen 6 SERDES IP - supports up to 112G LR ethernet with low power and latency