1.8V/3.3V I2C 5V Failsafe Failtolerant Automotive Grade 1 in GF (22nm)

32 bit - Compact RISC-V Processor Core

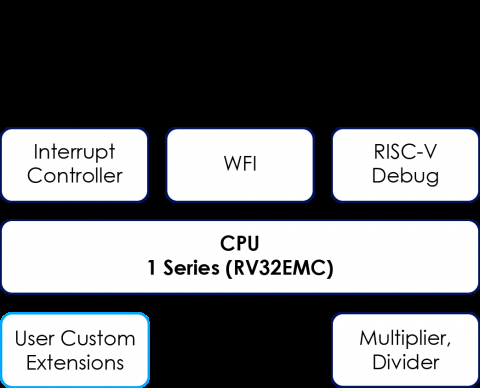

The core includes optional L1 data and instruction caches, optional instruction and data TCM, optional 8 or 16 PMP regions, an interrupt controller and RISC-V Debug module optionally with PC trace.

Like with all Codasip RISC-V cores, it is possible to create custom instructions using Codasip Studio to extend the L10 and to generate corresponding hardware and software development kits.

View 32 bit - Compact RISC-V Processor Core full description to...

- see the entire 32 bit - Compact RISC-V Processor Core datasheet

- get in contact with 32 bit - Compact RISC-V Processor Core Supplier

Block Diagram of the 32 bit - Compact RISC-V Processor Core

Processor IP

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications

- ARC-V RMX-500 power efficient 32-bit RISC-V processor for embedded applications

- RT-660-FPGA DPA-Resistant Hardware Root-of-Trust Security Processor for Govt/Aero/Defense FIPS-140

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Secure-IC Securyzr(TM) Cyber Escort Unit IP provides real time detection of sero day attacks on processor

- 32-bit Embedded RISC-V Functional Safety Processor