32-bit CPU IP core supporting ISO 26262 ASIL B level functional safety for automotive applications

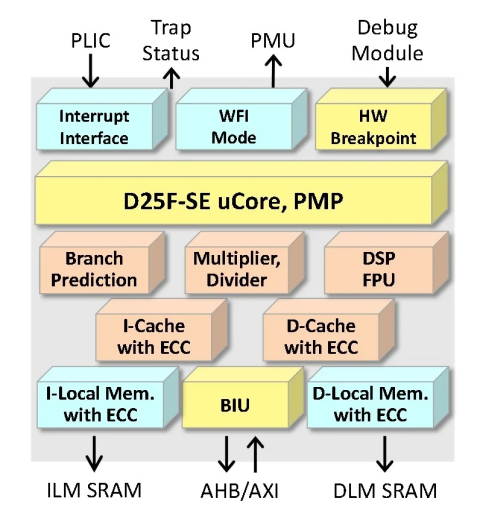

Based on AndeStar™ V5 architecture that incorporated RISC-V technology, D25F-SE is capable of delivering high per-MHz performance and operating at high frequencies with small gate count. It supports the RISC-V P-extension (draft) DSP/SIMD ISA contributed by Andes, single-/ double-precision floating point and bit-manipulation instructions, branch prediction for efficient branch execution, Instruction and Data caches, local memories for low-latency accesses, and ECC for memory error protection. Features also includes RISC-V Platform Level Interrupt Controller, AXI 64-bit or AHB 64/32-bit system bus, WFI mode for low power and power management, and JTAG debug interface.

View 32-bit CPU IP core supporting ISO 26262 ASIL B level functional safety for automotive applications full description to...

- see the entire 32-bit CPU IP core supporting ISO 26262 ASIL B level functional safety for automotive applications datasheet

- get in contact with 32-bit CPU IP core supporting ISO 26262 ASIL B level functional safety for automotive applications Supplier

Block Diagram of the 32-bit CPU IP core supporting ISO 26262 ASIL B level functional safety for automotive applications