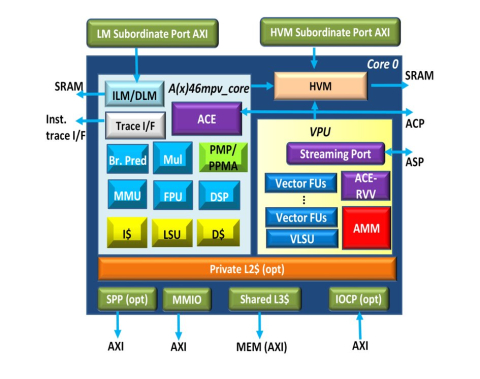

AndesCore™ A46MP(V) 32-bit multicore CPU IP is an 8-stage superscalar processor with Vector Processing Unit (VPU) based on AndeStar™ V5 architecture and Andes Matrix Multiply (AMM) extension. It supports RISC-V standard “G (IMA-FD)”, “ZC” compression, “B” bit manipulation, DSP/SIMD ‘P’ (draft), “V” (vector), CMO (cache management) extensions, Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions. It supports all RVA22 profile mandatory ISAs relevant for RV32. It features MMU for Linux based applications, dynamic branch prediction for efficient branch execution, dual-issue of common instruction pairs, level-1 private instruction/data caches, private level-2 cache and local memories for low-latency accesses. The A46MP(V) symmetric multiprocessor supports up to 16 cores and a shared level-3 cache controller. Coherence Manger ensures data coherence among CPU accesses and IO transactions from external bus managers. All caches are non-blocking with prefetch support. The A46MPV have a powerful VPU with up to 256b VLEN and Matrix unit, is excellent for computations involving large arrays of data.