5/10/40G Ultra Low Latency MAC PCS with AXI-4 and UCIe support

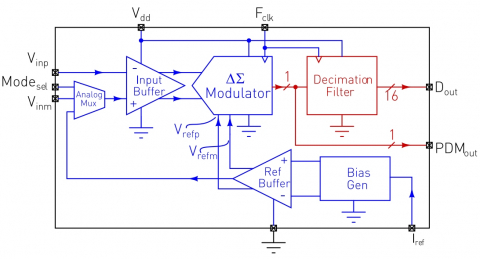

32-kHz Bandwidth Reconfigurable Delta-Sigma ADC providing up to 13 ENOB

The input impedance is resistive and hence can be easily driven by the preceding stage which may be another analog block or even directly a sensor. Furthermore, the input buffer can be configured to accept either

single-ended or differential voltage inputs making it more convenient to interface with single-ended output blocks/sensors.

The DSM outputs an oversampled single bit stream which is input to an internal decimation filter to filter off the high-frequency noise. The decimation

factor is configurable and hence the output data rate can be increased or decreased by trading off with performance as and when required. Additionally, aprovision is made to output both the 16-bit word from

the decimation filter and the oversampled 1-bit stream from the DSM, as and when demanded.

View 32-kHz Bandwidth Reconfigurable Delta-Sigma ADC providing up to 13 ENOB full description to...

- see the entire 32-kHz Bandwidth Reconfigurable Delta-Sigma ADC providing up to 13 ENOB datasheet

- get in contact with 32-kHz Bandwidth Reconfigurable Delta-Sigma ADC providing up to 13 ENOB Supplier

Block Diagram of the 32-kHz Bandwidth Reconfigurable Delta-Sigma ADC providing up to 13 ENOB

Delta-Sigma ADC IP

- 10-Bit 64MHz 1.2V 1.9mW delta-sigma ADC, CMOS 130nm

- 12-bit 40nm 1.1V 64MHz-to-340MHz continuous-time Delta-Sigma ADC

- 16 to 10 bit 32MSPS Delta-Sigma ADC

- 1-bit 2-channel 2.2 MSPS (8.5 kHz BW) delta-sigma ADC

- 9-bit 2-channel 0.5 to 33 MSPS (8 to 500 kHz BW) delta-sigma ADC

- 12-bit 800 kSPS cascade delta-sigma ADC