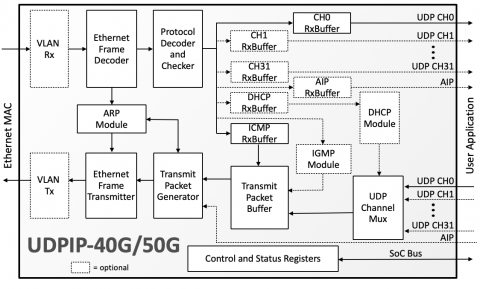

40G/50G UDP/IP Hardware Protocol Stack

Trouble-free network operation is ensured through run-time programmability of all the required network parameters (local, destination and gateway IP addresses; UDP ports; and MAC address). The core implements the Address Resolution Protocol (ARP), which is critical for multiple access networks, and the Echo Request and Reply Messages (“ping”) of the Internet Control Message Protocol (ICMP) widely used to test network connectivity. It can use a static IP address or automatically request and acquire an IP address from a Dynamic Host Configuration Server (DHCP) server. Furthermore, the core supports 801.1Q tagging, and is suitable for operation in a Virtual LAN.

The core is easy to integrate in systems with or without a host processor. Packet data can be read/written to the core via dedicated streaming-capable interfaces, or optionally via registers mapped on an SoC bus. The AMBA® AXI4-stream or the Avalon®-ST streaming protocols and the AMBA AHB and AXI, Avalon-MM, or Wishbone SoC bus protocols are supported. The core is Ethernet MAC-independent, but is available pre-integrated with a CAST, Altera, Xilinx, or other third-party eMAC core.

View 40G/50G UDP/IP Hardware Protocol Stack full description to...

- see the entire 40G/50G UDP/IP Hardware Protocol Stack datasheet

- get in contact with 40G/50G UDP/IP Hardware Protocol Stack Supplier

Block Diagram of the 40G/50G UDP/IP Hardware Protocol Stack