4K Video Scaler IP Core

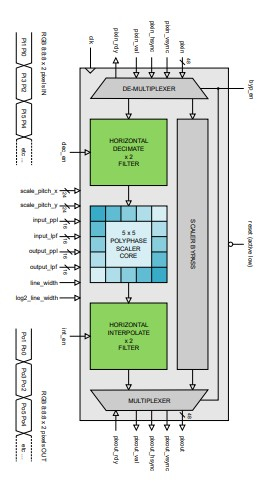

Internally, the video scaler is comprised of an input decimation section, a polyphase filter core section and an output interpolation section. In addition, the scaler is capable of processing two RGB pixels per clock and, as such, is able to support 4K+ pixel rates on most mid-range FPGA and SoC devices.

The polyphase filter core uses a 24-bit accumulator and a bank of polyphase FIR filters with 16 phases or interpolation points. All filter coefficients are programmable, allowing the user to define a wide range of filter characteristics if required. By default, the polyphase filter kernel uses a Lanczos2 windowed-sinc function that gives excellent all round performance.

Pixels flow into and out of the video scaler in accordance with a simple valid-ready streaming protocol. The scaler may also be easily adapted to use standard AXI4-stream interfaces which are popular with many vendors of FPGA, SoC and ASIC devices.

View 4K Video Scaler IP Core full description to...

- see the entire 4K Video Scaler IP Core datasheet

- get in contact with 4K Video Scaler IP Core Supplier

Block Diagram of the 4K Video Scaler IP Core IP Core