64-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux

View 64-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux full description to...

- see the entire 64-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux datasheet

- get in contact with 64-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux Supplier

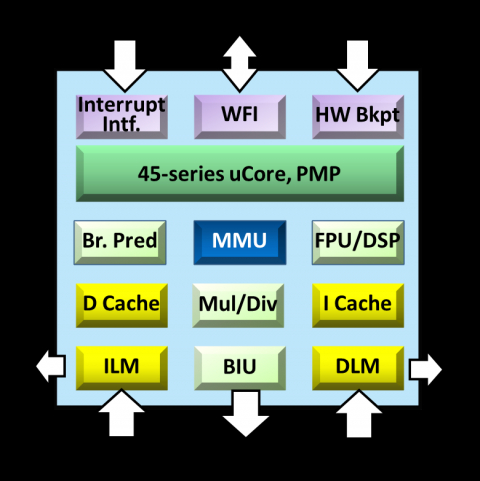

Block Diagram of the 64-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux

RISC-V; superscalar;dual-issue;8-stage pipeline;microprocessor;DSP IP

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP (DSP)

- 32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP and Linux

- 8-stage superscalar processor that supports ISO 26262 ASIL (Automotive Safety Integrity Level) -D level functional safety for automotive applications

- 64-bit RISC-V Multicore Processor with 1024-bit Vector Extension

- Compact, Secure and Performance Efficiency 32-bit RISC-V Core

- 32 bit RISC-V Multicore Processor with 256-bit VLEN and AMM