8-stage, dual-issue, highly efficient in-order pipeline compatible with the RISC-V RV64GCV ISA

View 8-stage, dual-issue, highly efficient in-order pipeline compatible with the RISC-V RV64GCV ISA full description to...

- see the entire 8-stage, dual-issue, highly efficient in-order pipeline compatible with the RISC-V RV64GCV ISA datasheet

- get in contact with 8-stage, dual-issue, highly efficient in-order pipeline compatible with the RISC-V RV64GCV ISA Supplier

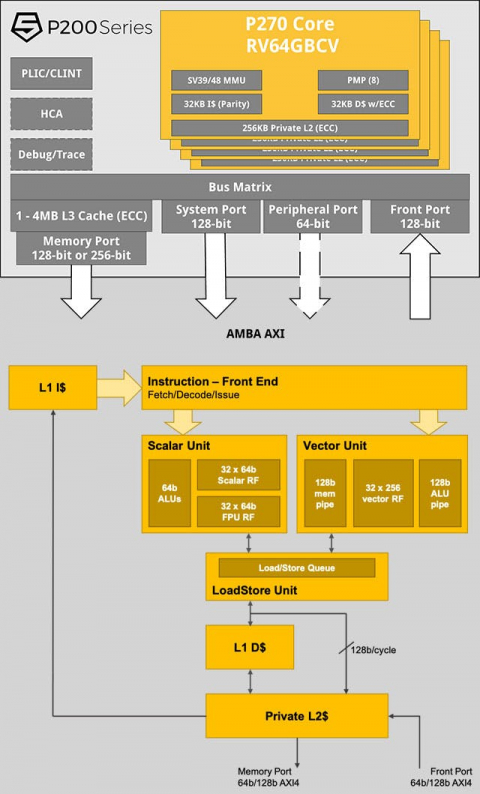

Block Diagram of the 8-stage, dual-issue, highly efficient in-order pipeline compatible with the RISC-V RV64GCV ISA

CPU IP

- High Bandwidth Out-of-Order RISC-V CPU IP Core

- All in one solution for AI in RISC-V

- 2D (vector graphics) GPU IP Further advanced architecture for minimized CPU load and increased pixel performance in vector processing

- 2D (vector graphics) & 3D GPU IP A GPU IP combining 3D and 2D rendering features with high performance, low power consumption, and minimum CPU load

- High Bandwidth In-Order RISC-V CPU IP Core

- RISC-V Processor - RV12 - 32/64 bit, Single Core CPU