5V Library for Generic I/O and ESD Applications TSMC 12NM FFC/FFC+

80251 IP

Each of our 80251 cores has a built-in support for Hardware Debug System, called DoCDTM. It is a real-time hardware debugger, which provides debugging capability of a whole System on Chip (SoC).

Unlike other on-chip debuggers, the DoCDTM provides non-intrusive debugging of running application. It can halt, run, step into or skip an instruction, read/write any contents of the microcontroller, including all registers, internal and external program memories and all SFRs, including user defined peripherals.

View 80251 IP full description to...

- see the entire 80251 IP datasheet

- get in contact with 80251 IP Supplier

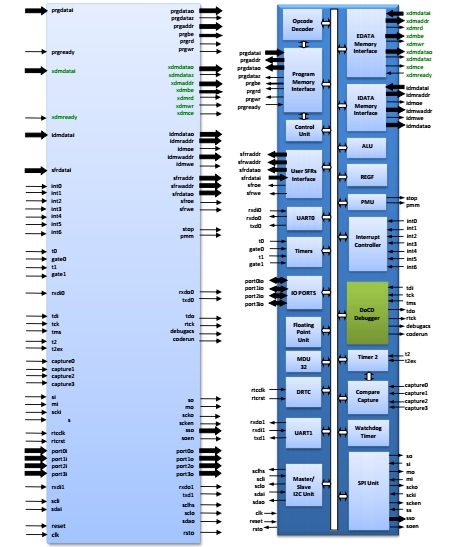

Block Diagram of the 80251 IP IP Core

80251 IP IP

- Super-Fast, Configurable 16-bit 80251 Microcontroller Core

- High Performance / Low Power Microcontroller Core

- Revolutionary Quad-Pipelined Ultra High Performance Microcontroller

- DES and Triple DES data encryption / decryption

- programmable SDRAM controller

- MIPI I3C Basic v1.1.1 specifications with Host Controller Interface v1.1 specification