AMBA Parameter Configurable Multi-Channel DMA Controller (typically 1 to 256)

8bits, 200Msps Sub-Ranging Flash AD Converter

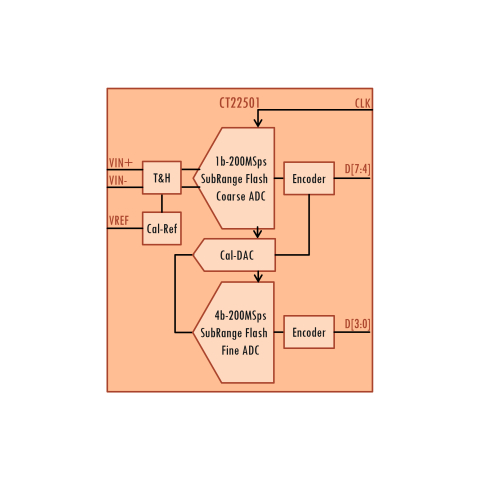

The conversion is thus carried out in 2 stages. The 4 most significant bits (MSBs) results from the operation of a Coarse Flash ADC. Its outputs are feed to a DAC in order to generate the inputs for the Fine Flash ADC (FADC) depending both on the input signal to be converted and on the results of the first part of the conversion.

The flash ADCs are implemented using dynamic latched comparators, in order to minimize static/DC power dissipation. In order to improve accuracy, self-calibration of the FADCs is employed. A redundant FADC is implemented so that calibration can be performed in background without stopping conversion, and is in power down while not converting and not performing calibration. Conversion takes 2 clock cycles.

CT22501 features a track and hold circuit that samples the input signal and feeds it to the flash ADCs.

View 8bits, 200Msps Sub-Ranging Flash AD Converter full description to...

- see the entire 8bits, 200Msps Sub-Ranging Flash AD Converter datasheet

- get in contact with 8bits, 200Msps Sub-Ranging Flash AD Converter Supplier

Block Diagram of the 8bits, 200Msps Sub-Ranging Flash AD Converter