Adaptive Clock Generation Module for DVFS and Droop Response

A 180nm Flip-Chip IO library with 1.2-1.8V GPIO, 1.8V & 5V analog/RF, 20-36V ultra-low leakage low-cap HV analog and OTP program cell

Built into our IO libraries and also offered as a separate service is our strong ESD expertise. Certus was founded by ESD engineers, and our results speak for themselves. We consistently exceed the ESD targets of 2KV HBM and 500V CDM and provide on-chip solutions for standards such as IEC-61000-4-2, system-level ESD, and Cable Discharge Events (CDE).

Certus supports IO libraries across multiple nodes, including 180nm, 130nm, 65nm, 40nm, 28nm, 22nm, and 16/12nm. Certus is particularly suited to providing custom variants in a cost-efficient framework. Please contact us for supplementary physical or electrical features that can suit your needs.

View A 180nm Flip-Chip IO library with 1.2-1.8V GPIO, 1.8V & 5V analog/RF, 20-36V ultra-low leakage low-cap HV analog and OTP program cell full description to...

- see the entire A 180nm Flip-Chip IO library with 1.2-1.8V GPIO, 1.8V & 5V analog/RF, 20-36V ultra-low leakage low-cap HV analog and OTP program cell datasheet

- get in contact with A 180nm Flip-Chip IO library with 1.2-1.8V GPIO, 1.8V & 5V analog/RF, 20-36V ultra-low leakage low-cap HV analog and OTP program cell Supplier

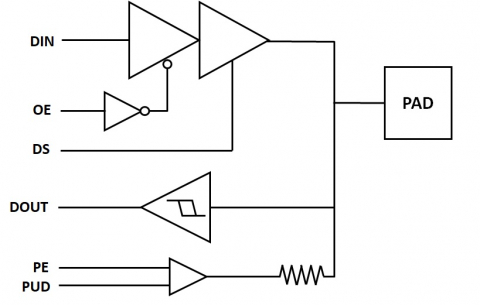

Block Diagram of the A 180nm Flip-Chip IO library with 1.2-1.8V GPIO, 1.8V & 5V analog/RF, 20-36V ultra-low leakage low-cap HV analog and OTP program cell

TSMC IP

- MIPI D-PHY IP for TSMC (5nm, 6/7nm, 12/16nm, 22nm, 28nm, 40nm)

- TSMC GF Intel Samsung Deskew Frequency Synthesizer PLL

- TSMC GF Intel Samsung Fractional-N Frequency Synthesizer PLL

- TSMC GF Intel Samsung Integer-N Frequency Synthesizer PLL

- TSMC Intel 32kHz Low-bandwidth Frequency Synthesizer PLL

- Complete USB Type-C Power Delivery PHY, RTL, and Software