AES Encrypt/Decrypt Core

Two architectural versions are available to suit system requirements. The Standard version (AES-S) is more compact, using a 32-bit datapath and requiring 44/52/60 clock cycles for each data block (128/192/256-bit cipher key, respectively). The Fast version (AES-F) achieves higher throughput, using a 128-bit datapath and requiring 11/13/15 clock cycles for each data block.

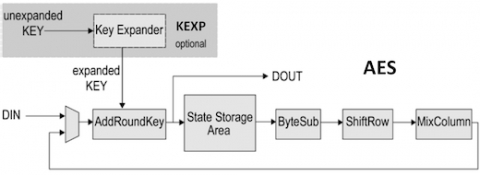

Various cipher modes can be supported (ECB, CBC, OFB, CFB, CTR, CCM, GCM and LRW). The core works with a pre-expanded key, or with optional key expansion logic.

The AES core is a fully synchronous design and has been evaluated in a variety of technologies. It is available optimized for ASICs or FPGAs, with complete deliverables.

View AES Encrypt/Decrypt Core full description to...

- see the entire AES Encrypt/Decrypt Core datasheet

- get in contact with AES Encrypt/Decrypt Core Supplier

Block Diagram of the AES Encrypt/Decrypt Core IP Core