AES IP Core

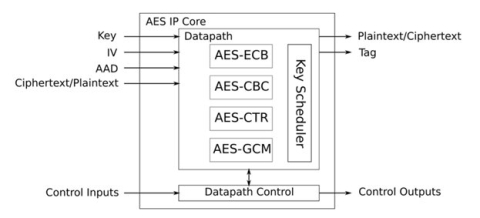

Countermeasures against side-channel attacks are implemented in the AES IP Core. Procenne AES IP Core is compatible with Xilinx FPGAs and INTEL FPGAs. VHDL is used as the Hardware Description Language of the IP Core. ECB, CBC, CTR, and GCM mode of operations are supported and implemented according to "NIST SP800-38a" and "NIST SP800-38d".

View AES IP Core full description to...

- see the entire AES IP Core datasheet

- get in contact with AES IP Core Supplier

Block Diagram of the AES IP Core IP Core

AES IP

- Secure-IC Securyzr™ Tunable Cryptography solutions with embedded side-channel protections: AES - SHA2 - SHA3 - PKC - RSA - ECC - ML-KEM - ML-DSA - XMSS - LMS - SM2 - SM3 - SM4 - Whirlpool - CHACHA20 - Poly1305

- Secure-IC's Securyzr™ Tunable AES (ECB, CBC, CTR, XTS, CCM, GCM) accelerator - optional SCA protection

- UFS 3.0 Host Controller with AES Encryption compatible with M-PHY 4.0 and UniPro 1.8

- 100G AES Encryption Core

- 10G/25G/40G/50G AES Encryption Core

- 400G AES Encryption Core