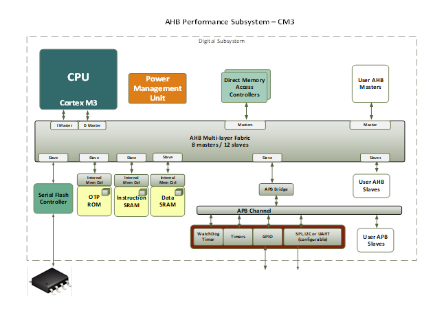

AHB Performance Subsystem - ARM M3

Additionally, the subsystem includes two DMA controllers for easily moving data from user peripherals to internal SRAM.

Most of the supported CPUs are powerful enough to handle applications such as spectral analysis, FFT, and data manipulation, thus making the subsystem a good choice for IoT devices where computation has to be done at the edge.

The AHB Performance Subsystem includes a standard set of peripherals and cores that supports RTOS and software kernels. Included is a QSPI, serial flash controller for boot loading program images or operating as an Execute in Place (XIP) engine using non-volatile external flash memory with low power.

The AHB Performance Subsystem is soft IP that can be used in all the popular semiconductor technology nodes.

View AHB Performance Subsystem - ARM M3 full description to...

- see the entire AHB Performance Subsystem - ARM M3 datasheet

- get in contact with AHB Performance Subsystem - ARM M3 Supplier

Block Diagram of the AHB Performance Subsystem - ARM M3

Performance IP

- 12bit 5Gsps silicon proven High performance Current Steering DAC IP Core

- High Performance Scalable Sensor Hub DSP Architecture

- Modern, high performance Audio DSP, optimized for far-field noise reduction and Artificial Intelligence speech recognition

- High Performance DDR5/4/3 Memory Controller

- 12-bit, 9 GSPS High Performance Swift™ DAC in 16nm CMOS

- 16bit 5Gsps silicon proven High performance Current Steering DAC IP Core