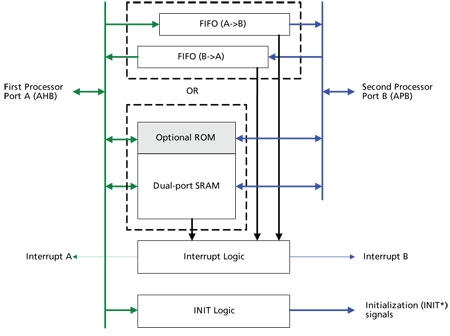

CoreMBX (Mail Box) allows data messages (mail) to pass back and forth from one processing element to another. The user is able to choose whether this message passing capability is implemented with one or more instances of dual-port SRAM hard macros, or with one or more instances of FIFO hard macros. The first processing element, such as Cortex-M1, connected to the first bus uses CoreMBX to initialize and pass messages back and forth to a second processing element, such as CoreABC or Core8051s, that uses a set of AMBA 2 or AMBA 3 advanced peripheral bus (APB) slave connections. Note that the first bus may be asynchronous to the second bus; therefore synchronization logic is included internally. CoreMBX Block Diagram