NVM OTP NeoBit in Vanguard (350nm, 250nm, 180nm, 160nm, 150nm, 110nm)

AMBA AHB Device/Host Bridge

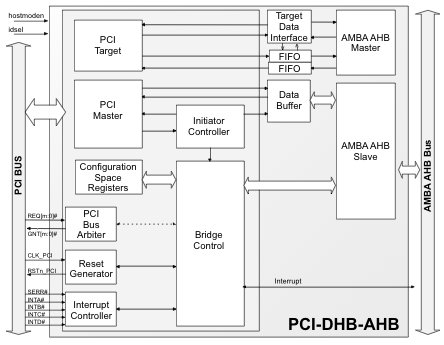

The bridge supports Host Mode and Device Mode (selected by a dedicated input pin). In Host Mode, the bridge is in charge of PCI bus arbitration and generating the PCI reset signal. In Device Mode, the bridge implements a PCI target enabling PCI access to the AMBA AHB bus space behind the bridge.

The bridge enables higher utilization of the bus’ available bandwidth by prefetching PCI data and buffering AHB data, and allows the host to initiate PCI accesses or to respond to transactions initiated by other PCI devices.

The AMBA AHB Device/Host Bridge complies with the PCI bus specification versions 3.0 and 2.3, and can act as a PCI master and target. Furthermore if implements PCI bus arbitration, supporting up to seven PCI bus agents, PCI reset signal generation, and all types of PCI transactions provisioned by the standard.

The host connects to the bridge via master and a slave 32-bit AMBA/AHB bus interfaces. The AHB slave interface allows the host to access the status and to control registers and initiate PCI Transfers, while data from the PCI target is communicated to the host via the AHB master interface.

The AMBA AHB Device/Host Bridge has been designed for straightforward reuse, with proven design practices that ensure easy integration and smooth technology mapping. The AMBA AHB Device/Host Bridge is available in synthesizable RTL or as a targeted FPGA netlist, and is delivered with everything required for rapid and successful integration and implementation.

View AMBA AHB Device/Host Bridge full description to...

- see the entire AMBA AHB Device/Host Bridge datasheet

- get in contact with AMBA AHB Device/Host Bridge Supplier

Block Diagram of the AMBA AHB Device/Host Bridge IP Core