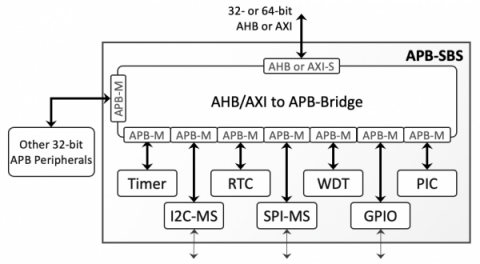

APB Subsystem

- I2C Master & Slave

- Single/Dual/Quad/Octal SPI Master & Slave

- 16550-compatible UART

- 32 GPIOs

- Real-Time Clock

- Watchdog Timer

- Generic Timer

- Programmable Interrupt Controller

Other peripherals with a 32-bit APB interface can be connected to the subsystem, via a configurable number of extra 32-bit APB ports. Each of the extra APB ports are configured independently to comply to APB2, APB3 or APB4 standard. The included bridge allows connecting the subsystem to a 32-bit or 64-bit AHB or AXI bus.

The APB-SBS was designed with industry best practices, and its reliability and low risk have been proven through both rigorous verification and customer production. It is delivered in human-readable Verilog source code along with comprehensive documentation for each module, example drivers, and software exercising all the peripherals.

This subsystem can be mapped to any Intel, Lattice, MicroSemi, or Xilinx programmable device, or to any ASIC technology, provided sufficient silicon resources are available. Please contact CAST Sales to get accurate characterization data for your specific implementation requirements.

View APB Subsystem full description to...

- see the entire APB Subsystem datasheet

- get in contact with APB Subsystem Supplier

Block Diagram of the APB Subsystem IP Core

APB IP

- FlexNoC 5 Network-on-Chip (NoC)

- FlexNoC Functional Safety (FuSa) Option helps meet up to ISO 26262 ASIL B and D requirements against random hardware faults.

- CodaCache® Last Level Cache IP

- LINFlexD Controller

- High Performance Second Generation Extended MIPI CSI2 Receiver

- WiSUN Sub-GHz 433, 868, 915MHz Transceiver IP