ARINC 818 Transceiver

The core has many flexible compile-time settings, allowing for various link speeds, line segmentations, and line-synchronization methods. It can be configured for various resolutions and pixel packing methods. Ancillary data can use default values set at compile time, or data can be updated in real time via register interface.

View ARINC 818 Transceiver full description to...

- see the entire ARINC 818 Transceiver datasheet

- get in contact with ARINC 818 Transceiver Supplier

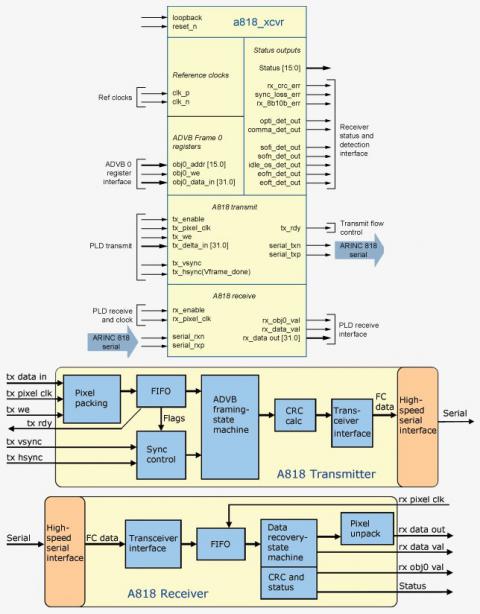

Block Diagram of the ARINC 818 Transceiver IP Core