AMBA Parameter Configurable Multi-Channel DMA Controller (typically 1 to 256)

ASIP-2

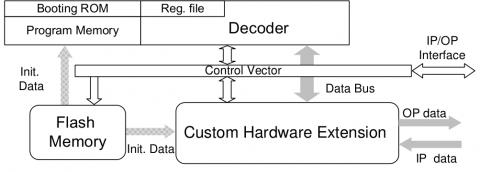

The engine is divided into two main parts: a processing element, which deals directly with the data, and an embedded processor to control the signal flow by configuring the processing element. The system architecture is shown in the Fig.

View ASIP-2 full description to...

- see the entire ASIP-2 datasheet

- get in contact with ASIP-2 Supplier

Block Diagram of the ASIP-2 IP Core

Reconfigurable IP

- Reconfigurable Parallel CRC Generator

- Low-power high-speed reconfigurable processor to accelerate AI everywhere.

- High Performance Media Processor

- PCIe 3.0, 2.1, 1.1 Controller supporting Root Port, Endpoint, Dual-mode Configurations, with AMBA AXI User Interface

- Low-power, low-gate-count, highly-configurable DSP core for audio and control processing

- High-Speed Digital PLL (0.5-7.5 GHz) in TSMC 40G CMOS