Software Defined Radio with Spread spectrum and SOQPSK for Telemetry applications

Avalon Multi-port SDRAM Memory Controller IP Core

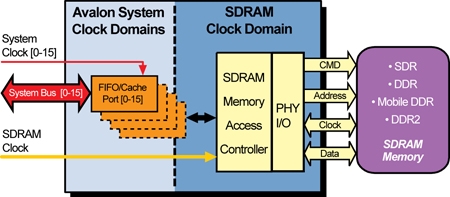

The Avalon Multi-port SDRAM Memory Controller slave ports can be independently clocked allowing the system to be partitioned and optimized to achieve maximum performance. Supporting post memory read and write cycles, the data FIFO's effectively double memory bandwidth on sequential address or FIFO cache hits. FIFO depth can be tailored for either streaming or random access.

The Avalon Multi-port SDRAM Memory Controller is optimized for Altera® Cyclone, Stratix, and Arria families of field programmable logic devices. The Avalon slave ports are configured with a SOPC Builder Ready component & Qsys GUI which greatly simplifies the design of Avalon-MM based SOC systems.

The SDRAM Memory Controller handles all memory tasks, including initialization and refresh cycles. It is designed to operate asynchronous to the local port clocks enabling the memory to be clocked at its peaked rated frequency maximizing system performance.

View Avalon Multi-port SDRAM Memory Controller IP Core full description to...

- see the entire Avalon Multi-port SDRAM Memory Controller IP Core datasheet

- get in contact with Avalon Multi-port SDRAM Memory Controller IP Core Supplier

Block Diagram of the Avalon Multi-port SDRAM Memory Controller IP Core