AMBA Parameter Configurable Multi-Channel DMA Controller (typically 1 to 256)

AXI to APB Bus Bridge

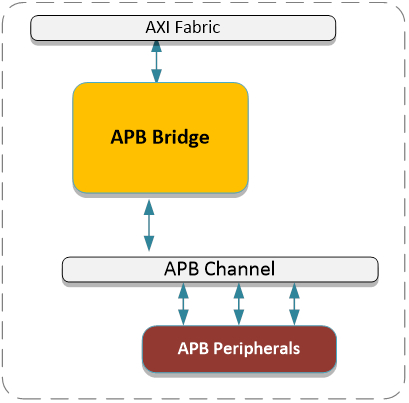

The AXI to APB Bridge acts as an AXI Slave, and an APB Master in an AXI/APB subsystem. Typically, the AXI to APB Bridge has its AXI interface connected to a Slave port on an AXI Channel/Interconnect module, and its APB interface connected to the Master port on an APB Channel module.

View AXI to APB Bus Bridge full description to...

- see the entire AXI to APB Bus Bridge datasheet

- get in contact with AXI to APB Bus Bridge Supplier

Block Diagram of the AXI to APB Bus Bridge IP Core

Bridge IP

- PCIe 5.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

- PCIe 4.0 Controller supporting Endpoint, Root Port, Switch, Bridge and advanced features

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- General Purpose & Bridge DMA

- RapidIO to AXI Bridge (RAB)

- Digital Capacitive Plus Bridge Sensor Interfaces