Bit Block Transfer (BitBLT) Graphics Engine IP Core

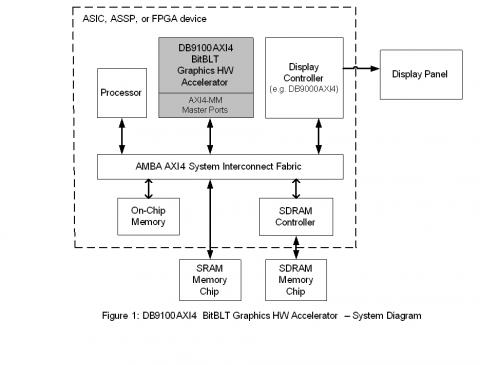

The Bit Block Transfer (BitBLT) Graphics Engine IP Core works in parallel with the TFT LCD Controller IP Core, interfacing a microprocessor and frame buffer memory via the AMBA AXI4 Bus to a TFT LCD panel. Frame buffer memory typically is either on-chip SRAM memory or larger off-chip SRAM or SDRAM.

View BitBLT Graphics Hardware Accelerator (AXI4 Bus) full description to...

- see the entire BitBLT Graphics Hardware Accelerator (AXI4 Bus) datasheet

- get in contact with BitBLT Graphics Hardware Accelerator (AXI4 Bus) Supplier

Block Diagram of the Bit Block Transfer (BitBLT) Graphics Engine IP Core