NVM OTP NeoBit in Vanguard (350nm, 250nm, 180nm, 160nm, 150nm, 110nm)

Block Viterbi Decoder

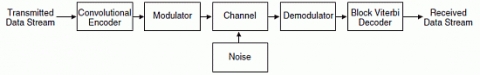

Lattice's Block Viterbi Decoder IP core is a parameterizable Viterbi Decoder for decoding different combinations of convolutionally encoded sequences. The decoder supports various code rates, constraint lengths, and generator polynomials. It also allows soft-decision decoding and is capable of decoding punctured codes. The core can operate in continuous or block modes, whichever is required by the channel. Either Tail Biting or Zero Flushing convolutional codes can be decoded in the block mode. All the configurable parameters, including operation mode, generator polynomials, punctured block size, and puncture pattern can be defined by the user to suit the needs of their application. The code rate and puncture pattern can also be changed dynamically through input ports during the operation of the decoder. Lattice’s Block Viterbi Decoder IP is compatible with many networking and wireless standards that use different methods of convolutional encoding at the encoder.

View Block Viterbi Decoder full description to...

- see the entire Block Viterbi Decoder datasheet

- get in contact with Block Viterbi Decoder Supplier

Block Diagram of the Block Viterbi Decoder IP Core

FPGA IP

- RT-630-FPGA Hardware Root of Trust Security Processor for Cloud/AI/ML SoC FIPS-140

- Complete USB Type-C Power Delivery PHY, RTL, and Software

- Ethernet TSN Switch IP Core - Efficient and Massively Customizable

- CXL 2.0 Agilex FPGA Acclerator Card

- PCIe Gen3 to SRIO Gen3 Bridge (FPGA)

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software