CAN Bus Controller with Message Filter (Mailbox concept)

The CAN Bus Controller contains 16 receive buffers, each one with its own message filter, and 8 transmit buffers with prioritized arbitration scheme. For optimal support of Higher Level Protocols (HLP) such as DeviceNet or SDC, the message filter covers the first two data bytes as well.

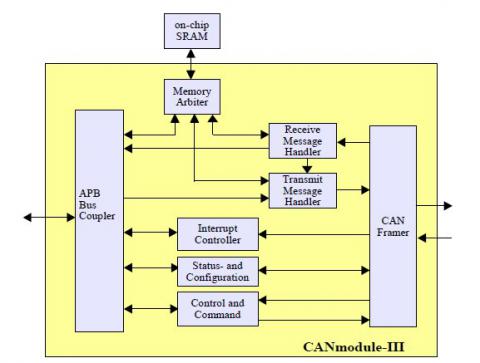

The design is written in technology independent HDL and can be mapped to ASIC and FPGA architectures and makes use of on-chip SRAM structures. An AMBA Advanced Peripheral Bus (APB) interface enables smooth integration into ARM based SOC’s. This full synchronous bus interface can easily be connect to other system buses.

View CAN Bus Controller with Message Filter (Mailbox concept) full description to...

- see the entire CAN Bus Controller with Message Filter (Mailbox concept) datasheet

- get in contact with CAN Bus Controller with Message Filter (Mailbox concept) Supplier

Block Diagram of the CAN Bus Controller with Message Filter (Mailbox concept)